ベース接地回路

この項目「ベース接地回路」は翻訳されたばかりのものです。不自然あるいは曖昧な表現などが含まれる可能性があり、このままでは読みづらいかもしれません。(原文:en:Common base 16:03, 11 May 2020(UTC)) 修正、加筆に協力し、現在の表現をより自然な表現にして下さる方を求めています。ノートページや履歴も参照してください。(2020年7月) |

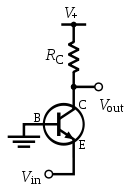

ベース接地回路(ベースせっちかいろ)またはベース共通回路(ベースきょうつうかいろ、英: Common base)は1段のバイポーラトランジスタを使った基本的な3種類の増幅回路構成の1つ。電流バッファや電圧増幅器として使われる。

この回路ではトランジスタのエミッタ端子が入力となり、コレクタが出力となる。ベースが出入力共通で用いられるためこの名前となっている。同様の構成を電界効果トランジスタで構築したものはゲート接地回路と呼ばれる。

単純化した動作

[編集]電流がエミッタに流れると、これにより電位差が生じ、トランジスタが導通する。コレクタを介して流れる電流は他の構成と同様にベース-エミッタ接合の電圧に比例する[1]。

それにより、エミッタに電流が流れない場合トランジスタは導通しない。

応用

[編集]この構成は低周波離散回路ではあまり一般的ではない。通常は例えば可動コイル型マイクロフォンのプリアンプとして機能するために異常に低い入力インピーダンスを必要とする増幅器(アンプ)に使われる。しかし、VHFやUHFなどの集積回路および高周波増幅器では、入力容量がエミッタ接地回路の帯域幅を低下させるミラー効果の影響を受けず入力と出力の間の絶縁が比較的高いため、一般的である。この高い絶縁は出力から入力へのフィードバックがほとんどないことを意味し、高い安定性につながる。

この構成は電流ゲインがほぼ1であるため(以下の式参照)、電流バッファとしても有用である。多くの場合この方法で用いられ、この前にエミッタ接地回路が1段置かれる。これら2つの組み合わせがカスコード構成を作り、高い入力インピーダンスや絶縁など各構成の利点をいくつか持っている。

低周波の特徴

[編集]低周波および小信号の条件のもとでは、図1の回路は図2の回路で表すことができ、BJTのハイブリッドπモデルが使われる。入力信号は直列抵抗Rsのテブナン電圧源vsで表され、負荷は抵抗RLである。この回路を用いて、以下のベース接地増幅回路の特性を得ることができる。

| 定義 | 式 | 近似式 | 条件 | |

|---|---|---|---|---|

| 開回路電圧利得 | ||||

| 短絡回路電流利得 | ||||

| 入力抵抗 | ||||

| 出力抵抗 |

- 注 平行線(||)は並列であることを示す。

一般的に、全体の電圧/電流利得は負荷効果により、上記の開回路/短絡利得(ソースおよび負荷抵抗に依存)よりも大幅に小さくことがある。

能動負荷

[編集]電圧増幅では、図1のように抵抗負荷RCを用いた場合、このアンプで許容される出力電圧振幅の範囲は電圧利得と関連する。これは大きな電圧利得には大きなRCが必要であり、RCでの大きなDC電圧降下を意味する。与えられた電源電圧に対してこの降下が大きいほどトランジスタのVCBが小さくなり、トランジスタの飽和が生じる前に許容される出力振幅が小さくなり、結果として出力信号にゆがみが生じる。この状況を避けるためには能動負荷、例えばカレントミラーを使うことができる。この選択をした場合、上表のRCの値は能動負荷の小信号出力抵抗(一般的に少なくとも図1の能動トランジスタのrOと同じ大きさである)に置き換えられる。これに対して能動負荷でのDC電圧降下は決まった低い値(能動負荷のコンプライアンス電圧)を持ち、抵抗RCを使用した同等の利得で発生するDC電圧降下よりもはるかに小さくなる。つまり、能動負荷の出力電圧振幅に対する制限が小さくなる。能動負荷であってもなくても、大きなAC利得は大きなAC出力抵抗と結びついているため、大きな負荷RL ≫ Routを除き出力での電圧分割は不十分になる。

電流バッファとして用いる場合、利得はRCの影響を受けないが、出力抵抗は影響を受ける。出力における電流分割により、駆動される負荷RLよりもはるかに大きいバッファの出力抵抗を持ち、大きな信号電流を負荷に送ることができるようにするのが望ましい。図1のように抵抗RCが使われる場合、大きな出力抵抗が大きなRCに結合され、出力での信号のゆれが制限される(電流が負荷に供給されたとしても通常、負荷への大電流信号は負荷にわたる大きな電流のゆれも意味する)。能動負荷は出力信号の振幅への深刻な影響がはるかに少ない、高いAC出力抵抗を提供する。

特徴の概観

[編集]いくつかの適用例を以下に詳しく説明する。簡単な概要は次の通り。

- エミッタノードに対する増幅器の入力インピーダンスRinは非常に低く、およそ次のように与えられる。

- ここでVTは熱電圧であり、IEはDCエミッタ電流である。

- 例えば、VT = 26 mVかつIE = 10 mAの場合、Rin = 2.6 &Omegaである。IEを下げてRinを大きくすると、トランスコンダクタンスが低くなる、出力抵抗が高くなる、βが低くなるなど他に考慮すべき結果がある。この低入力インピーダンスの問題に対する現実的な解決法は、入力に共通エミッタ段階を配置し、カスコード増幅器を形成することである。

- 入力インピーダンスが非常に低いため、ほとんどの信号源はベース共有増幅器のRinよりも大きい信号源インピーダンスを持っている。その結果、信号源が電圧源であっても電圧ではなく「電流」が入力に供給される(ノートンの定理によるとこの電流はおよそiin = vS / RSである)。出力信号も電流の場合、増幅器は電流バッファであり、入力と同じ電流を供給する。出力が電圧とみなされる場合、増幅器はトランス抵抗増幅器であり、負荷インピーダンスに依存した電圧を提供する。例えば抵抗負荷RLの値が増幅器の出力抵抗Routよりっもはるかに小さいときvout = iin RLである。つまり、この場合の電圧利得(以下で詳しく説明)は下式になる。

- 信号源インピーダンスでRS ≫ rEの場合、出力インピーダンスはRout = RC || [gm (rπ || RS) rO] に近づく。

- 非常に低いインピーダンスの信号源という特殊な場合では、ベース共通増幅器は以下で説明する例の1つである電圧増幅器として機能する。この(以下で詳しく説明する)RS ≪ rEかつRL ≪ Routの場合、電圧利得は次のようになる。

- ここでgm = IC / VTはトランスコンダクタンス。信号源インピーダンスが低い場合、Rout = rO || RC。

- ハイブリッドπモデルにrOを含めると、増幅器の出力からその入力への逆伝送が予測される。つまり増幅器は双方向的(biliteral)である。この1つの結果は入力/出力インピーダンスは負荷/信号源終端インピーダンスの影響を受けるため、例えば、出力抵抗RoutはrO || RC ≤ Rout ≤ (β + 1) rO || RCの範囲で変化する可能性があり、信号源抵抗RSに依存する。増幅器はrOの無視が正確(低い利得および低から中程度の負荷抵抗に対して有効)である場合、一方向的として近似することができ、解析を単純化できる。この近似は分離設計で行われることが多いが、能動負荷が通常使われるRF回路や集積回路設計で精度が低下する可能性がある。

電圧増幅器

[編集]

ベース接地回路を電圧増幅器として使用する場合の回路を図2に示す。

出力抵抗は大きく、少なくともRC || rOであり、この値は低い信号源インピーダンス(RS ≪ rE)で生じる。大きい出力抵抗は出力での分圧の低下につながるため、電圧増幅器では望ましくない。それでもなお、電圧利得は小さい負荷でも感知できる。表によるとRS = rEの場合、利得はAv = gm RL / 2である。もっと大きい信号源インピーダンスの場合、利得は抵抗比RL / RSで決まり、トランジスタの特性によらない。このことは温度やトランジスタの変化に敏感でないことが重要な場合に利点となる。

これらの計算にハイブリッドπモデルを使用する代わりの手法は、二端子対回路に基づく一般的な手法である。例えばこのように電圧が出力である用途では、出力端子で電圧増幅器を使用するためg等価の2端子を選択して単純化することができる。

RSがrE近くの値の場合、増幅器は電圧増幅器と電流バッファの間で移行的である。RS >> rEの場合、テブナン電圧源としてのドライバ表現は、ノートン電流源による表現で置き換える必要がある。次で説明するように、ベース接地回路は電圧増幅器のように動作するのをやめ電流フォロワのように動作する。

電流フォロワ

[編集]

図3は電流フォロワとして使用されるベース共有増幅器を示している。回路信号は入力のACノートン電流源(電流IS、ノートン抵抗RS)により提供され、回路は出力に抵抗負荷RLを持つ。

前述のようにこの増幅器は出力を入力に接続する出力抵抗rOの結果として双方向的である。このとき、最悪の場合でも出力抵抗は大きくなる(少なくともrO || RCであり、大きいRSの場合(β + 1) rO || RCになる)。好ましい電流分割がほとんどの電流を負荷に送るため、大きな出力抵抗が電流源の望ましい属性である。電流利得はRS ≫ rEである限りほぼ1である。

代わりの解析手法は二端子対回路に基づくものである。例えば、このように電流が出力である用途では出力端子で電流増幅器を使用するため、h等価の2端子が選択される。

関連項目

[編集]脚注

[編集]- ^ “Transistor Operating Details”. hyperphysics.phy-astr.gsu.edu. 2020年7月閲覧。

外部リンク

[編集]- Basic BJT Amplifier Configurations (archived from the original on September 9, 2007)

- NPN Common Base Amplifier — HyperPhysics

- ECE 327: Transistor Basics — Gives example common base circuit (i.e., current source) with explanation.

![{\displaystyle R_{C}\|\left([1+g_{m}(r_{\pi }\|R_{S})]r_{o}+r_{\pi }\|R_{S}\right)}](https://wikimedia.org/api/rest_v1/media/math/render/svg/1bf6a1b87e6cff035260a4a4ce04dced5d5e3d51)

![{\displaystyle {\begin{aligned}&R_{C}||r_{o}\\&R_{C}||\left(r_{o}\left[1+g_{m}\left(r_{\pi }||R_{S}\right)\right]\right)\end{aligned}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f9729b069c8324bf864d38d3ce5d077858d0ab0b)