カレントミラー

カレントミラー(英 : Current mirror)とは、能動素子を用いて他の回路に流れる参照電流をコピーし、負荷にかかわらず出力電流を参照電流と同じ値に保つことができる電子回路である。その「コピー」される電流は時に信号電流であってもよい。

概念的には、理想的なカレントミラー回路は電流方向を逆にする理想的な「反転電流増幅回路」である。あるいは、電流制御電流源(CCCS)であるとも言える。カレントミラーはバイアス電流と能動負荷を回路に供給するためだけに用いられるのでなく、より現実的な電流源のモデルとしても用いられる(理想的な電流源は存在しないため)。

ここで扱う回路構成は、多くの半導体集積回路で用いられているものであり、それは出力トランジスタ側でのエミッター減衰抵抗のないワイドラー電流源に相当する。この構成は、集積回路でのみ用いられる。なぜなら、2つのトランジスタの特性が極めて近くなければならず、それはディスクリート素子では実現不可能だからである。

他の回路構成としては、ウィルソン・カレントミラー回路がある。このウィルソン回路はアーリー効果に起因する問題を低減することができる。

特徴

[編集]カレントミラー回路を特徴づけるものとしては、以下の3つの特性がある。

一つ目は、伝達比(電流増幅回路の場合)あるいは出力電流強度(定電流源の場合)である。

二つ目は、出力電流が負荷に対してどの程度変動するかを決定する交流出力抵抗である。

三つ目は、正常動作をするのに必要なミラー出力部における最低電圧降下である。この最低電圧は、ミラー回路の出力トランジスタがアクティブ動作を保つのに必要な電圧である。ミラー回路が正常動作する電圧範囲を許容範囲(コンプライアンス範囲)と呼び、回路が正常/不良動作をするその境界の電圧を許容電圧(コンプライアンス電圧)と呼ぶ。ミラー回路は、温度変化に対する安定性などのたくさんの二次的な性能を決める要因がある。

実用上の近似

[編集]小信号解析では、カレントミラー回路はノートン等価回路として近似される。

大信号解析では、カレントミラー回路は通常、単純に理想的な電流源として近似される。しかし、理想的な電流源はいくつかの点において非現実的である:

- 無限大の交流インピーダンスを持つこと(実際のミラー回路は有限のインピーダンスを持つ)。

- 電圧にかかわらず一定の電流を供給すること。つまり、許容電圧が存在しないこと。

- 周波数制限が存在しないこと(実際のミラー回路はトランジスタの寄生容量によって制限が存在する)。

- 環境(例えばノイズ、電源電圧の変動、素子の公差など)に対して影響を受けないこと。

カレントミラー回路の実現

[編集]基本的な考え方

[編集]バイポーラトランジスタは最も簡単な電流-電流変換器であるが、その伝達比は温度変化、βの公差に大きく依存する。これらの変動を除去するために、カレントミラー回路は同じ条件で配置された2つの電流-電圧変換器、電圧-電流変換器をカスケード接続している。

これらの変換器は必ずしも線形動作である必要はなく、必要なことはただその特性が対称的であることである(例えば、以下で見るようにバイポーラトランジスタでのカレントミラー回路では、出力は入力に対して対数的な変化であったり指数的な変化である)。

通常、二つの同一の変換素子が用いられるが、片方の素子の特性は負のフィードバックをかけることによって反転することができる。例えば、バイポーラトランジスタのベース-エミッタ間に電圧を入力し、コレクタ電流を出力する場合を考えると、トランジスタは入力に対して指数関数的に出力が変化する電圧-電流変換器となる。入力に負のフィードバック(簡単にはベースとコレクタを接続)を行う事でトランジスタ動作を「反転」することができ、対数的に出力が変化する電流-電圧変換器となる。つまり所望のコレクタ電流が流れるように「出力」であるベース-エミッタ間電圧が自動的に決定されるということである。

したがって、カレントミラー回路は2つの等価な変換器(一つは反転動作、もう一つは通常動作)のカスケード接続から構成されていると言える。

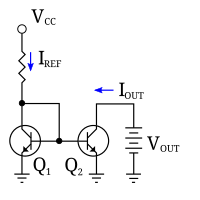

バイポーラトランジスタを用いた基本的なカレントミラー回路

[編集]

最も簡単なバイポーラカレントミラー回路(図1)はこの考え方によって構成されている。 これは二段のカスケード接続されたトランジスタからなり、トランジスタQ1, Q2はそれぞれ反転動作 / 通常動作の電圧-電流変換器としての役割を果たしている。

トランジスタQ1のエミッタは接地されていて、コレクタ-ベース間電圧は0である。このため、Q1の電圧降下はVBEで、この電圧はダイオード方程式に従って決められる。また、Q1のこの接続方法は、ダイオード接続と呼ばれている(Ebers-Mollモデルも参照のこと)。

回路中で単にダイオードではなく、トランジスタQ1を用いることは重要である。なぜなら、Q1はQ2におけるVBEも決定するからである。もしQ1とQ2の特性がほぼ等しい場合、またQ2のVCBが0になるようにミラー回路出力電圧VOUTを選べば、Q1によって決定されたVBEの値により、Q2を流れるエミッタ電流はQ1を流れるエミッタ電流と等しい値になる。Q1とQ2の特性が等しいので、β0についてもまた等しく、ミラー出力電流もQ1のコレクタ電流と等しくなる。

ミラー回路による出力トランジスタを流れる電流は、任意のコレクタ-ベース間電圧VCBに対して、以下の式で与えられる。

ここで、ISは逆飽和電流、あるいは規格化電流、VTは熱電圧、VAはアーリー電圧である。この電流はQ2がVCB =0 Vを満たすのであれば、参照電流Irefと以下の式で対応付けられている。

この式はQ1のコレクタに節点に対してキルヒホッフの法則を適用することで得られる。

参照電流IrefはQ1にコレクタ電流を、Q1, Q2の両方にベース電流を供給している。ここで、Q1, Q2のVCBが共に0であれば、これらのベース電流は等しく、IB1 = IB2 = IBである。したがって、

を得る。ここで、電流増幅率β0はVCB =0 VにおけるQ1, Q2のβの値である。

出力抵抗

[編集]もし出力トランジスタQ2でのVBCが0よりも大きい値であれば、Q2のコレクタ電流はアーリー効果によってQ1でのコレクタ電流よりもいくらか大きい値になる。言い換えれば、ミラー出力は有限の出力抵抗roを有することになる。すなわち、

ここで、VAはアーリー電圧であり、VCEは出力トランジスタのコレクタ-エミッタ間電圧である。

許容電圧

[編集]出力トランジスタQ2をアクティブ動作に保つためには、VCB ≥ 0 Vが必要である。従ってQ2がVCB = 0 Vを満たし、かつコレクタ電流ICを出力する状態というのは、これは正常なミラー動作をするのに必要な最低出力電圧、つまり許容電圧VCVがVOUT = VCV = VBEであることを意味する。従って上記のI-V関係を式変形することで、以下を得る:

ここでVTは熱電圧であり、ISは逆飽和電流、あるいは規格化電流である。

拡張・より複雑な場合

[編集]トランジスタQ2がVCB > 0 Vを満たすとき、トランジスタの特性はもはや一致していない。特に、βは以下のようにアーリー効果によって異なってしまう。

ここで、VAはアーリー電圧、β0はVCB = 0 Vの時のβの値である。β0は流れる電流の大きさに依存し、そして今二つのトランジスタは異なる電流が流れているため、アーリー効果の違いに加えβ0の値も異なるであろう。(Gummel–Poonモデルも参照のこと)。

更に、流れる電流の違いによりQ2はQ1よりも消費電力が大きく、より熱を発するかもしれない。2つのトランジスタの特性を同じに保つには、トランジスタの温度はほぼ等しくなければならない。集積回路や同じシリコンダイに載っているトランジスタアレイにおいては、これは容易に実現できる。しかしながら、もしも二つのトランジスタの距離が大きく離れている場合には、カレントミラー回路の精度が犠牲になってしまうだろう。

同じ特性を持つトランジスタを幾つか同じベース端子に追加して接続することで、コレクタ電流を複数回コピーすることは可能である。 しかしながら、右半分のトランジスタのベース電流は0ではないため、それぞれの追加した右半分のトランジスタはQ1から少しばかりのコレクタ電流を「盗む」ことには注意しなければならない。これによって、出力電流は設計した電流値よりも少し小さい値になってしまうだろう。

ミラー抵抗を大きくするためのエミッター減衰抵抗を用いたミラー回路の例も参照のこと。

図に示されている簡単なミラー回路においては、典型的なβの値では出力電流の誤差は1%以内である。

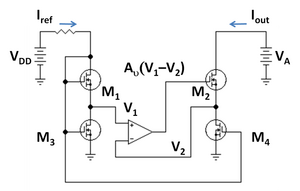

MOSFETを用いた基本的なカレントミラー回路

[編集]図2に示すように、基本的なカレントミラー回路はMOSFETを用いることでも構成することができる。トランジスタM1は飽和領域、あるいはアクティブ領域にあり、M2についても同様である。この構成では、以下で示すように出力電流IOUTとIREFとの関係は陽に表すことができる。

MOSFETのドレイン電流IDは、ID = f (VGS, VDG)で与えられるようにゲート-ソース間電圧VGS及びドレイン-ゲート間電圧VDGの関数であり、これはMOSFETデバイスの特性から導出される。

カレントミラー回路におけるM1を流れる電流は、ID = IREFである。参照電流IREFは既知の値を持つ電流であり、以下で示すように抵抗によって供給されたり、あるいは電源電圧の変動に対して一定であることを保証するために、「閾値電圧参照型」や「自己バイアス型」の電流源が用いられる[1]

M1はVDG = 0とすると、ID = f (VGS, 0) = IREFで表されるようにIREFはVGSと一対一の対応がつく。したがってIREFは、VGSの値を一意に決定する。

図2の回路ではM2にもM1と同じ大きさのVGSが印加されている。もしもM2もまたVDG = 0であり、そしてM1とM2の特性(例えばチャネル長、幅、閾値電圧など)がほぼ等しい場合には、出力側でもIOUT = f (VGS, VDG = 0) = IREFという電流を得ることができる。つまり、出力側でVDG = 0であり、両者のトランジスタが同じ特性であれば、出力電流は参照電流と同じになる。

ドレイン-ソース間電圧は、VDS = VDG + VGSで表される。この式を代入することで、Shichman-Hodgesモデルによってf (VGS, VDG)の近似的な関数が与えられる[2]。

ここで、μnは電子移動度、COXはゲート酸化膜容量、W/Lはチャネルの幅と長さの比、λはチャネル長変調係数である。

出力抵抗

[編集]チャネル長変調効果により、ミラー回路はroで表される有限の出力抵抗(ノートン抵抗)を有する(チャネル長変調効果も参照のこと)。つまり、

である。

許容電圧

[編集]出力トランジスタの抵抗を高くするには、VDG ≥ 0 Vが必要である[nb 1](こちらの書籍も参照のこと[3])。出力トランジスタがVDG = 0 Vを満たし、電流を出力している状態においては、これはミラー動作を行える最低出力電圧、つまり許容電圧がVOUT = VCV = VGSを満たすことを意味する。したがって、逆関数f −1を用いることで、以下を得る。

Shichman-Hodgesモデルにおいては、f−1は平方根の関数として近似することができる。

拡張及び制限

[編集]このタイプのミラー回路の利点は、関数fがデバイス幅Wに対して線形変化するということであり、Shichman-Hodgesモデルよりもさらに正確なモデルにおいてもほぼ線形性は満たされる。したがって、二つのトランジスタ幅の比をそれぞれ調整することによって、参照電流値の整数倍の大きさの電流を生成することが可能である。

Shichman-Hodgesモデル[4]は一世代前のトランジスタ技術においてのみ正確であるが、今日においてもその簡潔さからよく用いられている。近年ではより現実的なモデルに基づいてコンピュータでのシミュレーションによって電流電圧特性を計算する。この現実的なモデルでは、VGS依存性が二乗則に従わない、VDS依存性が単にλVDSで表されていない、という違いがある。その他の現実に即していない式としては、性能のチャネル長Lに関する依存性がある。GrayやMeyerらによって指摘されているように、L依存性に大きく寄与しているのはλである。彼らは、λは通常実験データから決定されなければならない、と指摘している[5]。

個々のデバイス間でさえも閾値電圧Vthは大きな分散があるため、ディスクリートな部品でカレントミラー回路を構成するのは問題がある。ソース減衰抵抗によってこの分散が幾分補償されたとしても、その抵抗値は非常に大きくなるため、出力抵抗が(小さくなることによって)犠牲になる。従って、MOSFETでのカレントミラー回路は集積回路、または同一基板上でのものに限られる。

フィードバック強化型カレントミラー

[編集]

図3には出力抵抗を大きくするために負帰還を加えたカレントミラー回路が示してある。オペアンプがあることによって、これらの回路はゲイン増強型カレントミラー回路と呼ばれることもある。あるいは許容電圧が比較的低いため、ワイドスイング型カレントミラー回路と呼ばれることもある。とりわけMOSFETを用いたミラー回路では、この考えに基づいた様々な回路が用いられる[6][7][8]。なぜなら、MOSFETはそれ自体の出力抵抗がそもそも小さいからである。図4にはMOSFETを用いたゲイン増強型カレントミラー回路が示されている。ここで、M3とM4は線形領域で動作しており、図3におけるエミッター抵抗REと同じ役割を果たしている。M1とM2は飽和領域で動作しており、図3におけるQ1とQ2と同じ役割を果たしている。図3の回路がどのような動作をするかは以下の通りである。

オペアンプには、抵抗REに接続されているQ1, Q2のエミッター端の電圧差V1 − V2が入力される。この電圧差はオペアンプによって増幅され、出力トランジスタQ2のベースに出力する。もしもVBEが増大すると、Q2を流れる電流は増大し、REの電圧降下が大きくなるためV2も増大し、V1 − V2は小さくなる。結果的に、Q2のベース電圧は小さくなり、Q2のVBEも減少し、出力電流の増大が相殺されることになる。

オペアンプのゲインAvが十分大きいのであれば、ほんの僅かな電圧差V1 − V2によってQ2のベース電圧VBを十分供給することができる。つまり、

従って、REを流れる電流はほぼ等しく、ミラー出力もQ1におけるコレクタ電流IC1とほぼ同じ値になる。IC1は、参照電流IREFによって以下のように決定される。

ここで、もしもQ2のVBCが0でないのであれば、Q1 のβ1とQ2のβ2の値はアーリー効果によって異なっている。

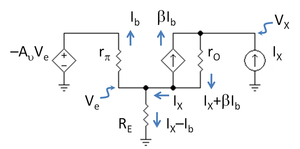

出力抵抗

[編集]

出力抵抗の理想的な取り扱いは注釈を参考のこと[nb 2]。上記の議論の理想的な場合、つまりオペアンプのゲインが無限大である場合の表式は以下の通りである。有限のゲインAvを持つオペアンプ以外はすべて理想的な素子を用いた小信号回路は図5の通りである(β, ro, rπ はいずれもQ2のパラメータである)。図5の等価回路を導出するにあたり、図3のオペアンプの正端子への入力は交流的に接地されているため、オペアンプへの入力は負端子に単にエミッタ電圧Veが入力されており、したがって出力で電圧は−Av Veである。オームの法則を入力抵抗rπに適用することで、小信号ベース電流Ibは以下のように表される。

この結果とREに関するオームの法則と合わせることで、Veは消去することができ、以下を得る[nb 3]。

ソースから電流IXが流れ込んだ時のグラウンドまでの電圧降下の大きさは、キルヒホッフの法則より以下で与えられる。

Ibを代入し、式変形を行うことで、出力抵抗Routは以下のようになる。

ゲインが非常に大きい場合(Av ≫ rπ / RE)、この回路で得られる最大の出力抵抗は、

である。この値は、基本的なミラー回路の出力抵抗Rout = roと比べて非常に大きな値である。

図4のMOSFETを用いた場合の小信号等価回路は、バイポーラの場合でβ = gm rπとし、rπ → ∞を考えることで得られる。つまり、

である。ここで、REはソース端のMOSFET M3, M4の抵抗値である。しかし図3の回路と異なり、ゲインAvが大きくなるにつれ(REは固定)Rout は大きくなるため、Avが十分大でも極限値まで達しない。

許容電圧

[編集]図3では、オペアンプの非常に大きなゲインによってほんの小さな抵抗REから大きな出力抵抗を得ていた。REが小さいということは、V2 もまた小さいということであり、ミラー回路にとっては許容電圧が小さいということである。これは、単純なバイポーラ・カレントミラー回路での許容電圧よりもほんの少しだけ大きな値である。このような理由から、このタイプのカレントミラー回路はワイドスイングカレントミラー回路と呼ばれる。なぜなら、許容電圧を大きくすることを犠牲にして高い出力抵抗Rout を得るような他のカレントミラー回路と比べて、出力電圧スイングを大きくできるからである。

図4のMOSFET回路では、図3の回路のようにオペアンプのゲインAvが大きくなるにつれてREを小さくすることができる(Routを一定のまま)ので、ミラー回路の許容電圧を低くすることができる。

その他のカレントミラー回路

[編集]基本的なミラー回路よりも高い出力抵抗が得られるようなカレントミラー回路(出力電圧とは独立で電流出力が決まる理想的なミラー回路を目指す試みである)や、温度変化、デバイスパラメータの分散、電源電圧の変動に対して出力電流が影響されにくいカレントミラー回路はたくさんある。これらの複数のトランジスタを用いたミラー回路はバイポーラトランジスタ、MOSFETの両方が用いられる。これらの回路には以下のようなものがある。

- ワイドラー電流源

- 電流源としてのウィルソンカレントミラー回路

- カスコード型電流源

注釈

[編集]- ^ 出力抵抗を大きく保つことは、MOSFETを飽和領域に保つこと以上の意味がある。それは、実際のMOSFETの出力抵抗は飽和領域に入る時にだけ増加しはじめ、そしてVDG ≥ 0 Vのときにのみ最大値に近くなるまで増加するからである。

- ^ もしオペアンプを電圧V1 = V2であるようなヌラーで置き換えた場合、ソース端を流れる電流は一定値に保たれる。これは、トランジスタのエミッタ電流も同じであることを意味する。もしもQ2のVCBが増加したとき、出力トランジスタのβもアーリー効果によって増大する:β = β0(1 + VCB/VA)。結果として、IB = IE / (β + 1) で与えられるQ2のベース電流は減少し、出力電流IOUT = IE / (1 + 1 / β) はわずかに増大する(βがわずかに増大するため)。これを数式で書くと、以下のようになる

- ここで、トランジスタの出力抵抗はro = (VA + VCB) / IOUTで与えられる。つまり、理想的なオペアンプヌラーを用いた理想的なミラー回路の出力抵抗は、ROUT = (β + 1)ro で与えられる。これは、後にゲインを無限大にして得られる結果と一致する。

- ^ Av → ∞に近づくにつれ、Ve → 0 、Ib → IXに近づく。

関連項目

[編集]- 電流源

- ワイドラー電流源

- ウィルソンカレントミラー

- バイポーラトランジスタ

- MOSFET

- チャネル長変調効果

- アーリー効果

引用文献

[編集]- ^ Paul R. Gray; Paul J. Hurst; Stephen H. Lewis; Robert G. Meyer (2001). Analysis and Design of Analog Integrated Circuits (Fourth ed.). New York: Wiley. p. 308–309. ISBN 0-471-32168-0

- ^ Gray. Eq. 1.165, p. 44. ISBN 0-471-32168-0

- ^ R. Jacob Baker (2010). CMOS Circuit Design, Layout and Simulation (Third ed.). New York: Wiley-IEEE. pp. 297, §9.2.1 and Figure 20.28, p. 636. ISBN 978-0-470-88132-3

- ^ NanoDotTek Report NDT14-08-2007, 12 August 2007 Archived 17 June 2012 at the Wayback Machine.

- ^ Gray. p. 44. ISBN 0-471-32168-0

- ^ R. Jacob Baker. § 20.2.4 pp. 645–646. ISBN 978-0-470-88132-3

- ^ Ivanov V. I., Filanovksy I. M. (2004). Operational amplifier speed and accuracy improvement: analog circuit design with structural methodology (The Kluwer international series in engineering and computer science, v. 763 ed.). Boston, Mass.: Kluwer Academic. p. §6.1, p. 105–108. ISBN 1-4020-7772-6

- ^ W. M. C. Sansen (2006). Analog design essentials. New York; Berlin: Springer. p. §0310, p. 93. ISBN 0-387-25746-2

外部リンク

[編集]- 4QD tec - Current sources and mirrors Compendium of circuits and descriptions

![{\displaystyle R_{\text{out}}=r_{\rm {o}}\left[1+g_{m}R_{\rm {E}}(A_{v}+1)\right]+R_{\rm {E}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/f5bbed03737d4668b905b6829ed8f45d898090c5)