電界効果トランジスタ

電界効果トランジスタ(でんかいこうかトランジスタ、Field effect transistor, FET)は、半導体の内部に生じる電界によって電流を制御する方式のトランジスタである。

微細かつ平面的なものを大量に製造する技術が確立されており、集積回路に搭載されている半導体素子としては最も一般的である。一般的なスマートフォンやパーソナルコンピュータに搭載されているCPUには、1億個以上のFETが組み込まれている。

この記事では主にSiなどの無機半導体によるものについて述べる。有機半導体を用いたものについては有機電界効果トランジスタを参照。

概要

[編集]FETは、ゲート電極に電圧を加えることでチャネル領域に生じる電界によって電子または正孔の密度を制御し、ソース・ドレイン電極間の電流を制御するトランジスタである。トランジスタの動作原理には大きく分けて二つの方式があり、電子と正孔の2種類のキャリアの働きによるバイポーラトランジスタに対して、FETはいずれか1種類のキャリアだけを用いるため、ユニポーラトランジスタと呼ばれる。 FETは、制御点であるゲートへの電圧駆動で動作する。対してバイポーラトランジスタはベースに対する電流駆動である。

製作方法と構造での主な種類として、接合型FET(ジャンクションFET, JFET,J-FET)とMOSFETに大別される。さらにゲート電極に金属素材を用いたMESFETがある。 チャネルの種類による分類でn型とp型が存在する。

端子

[編集]

FETには主な3種類の端子「ゲート」「ソース」「ドレイン」がある。ジャンクションFETは通常、以上の3端子のみを持つ。

MOSFETでは「ゲート」「ソース」「ドレイン」「バックゲート/バルク/サブストレート/ボディ(半導体チップ基板で呼称が一定していない)」の4端子で構成される。チャネルの種類によりp型チャネルの PMOSとn型チャネルのNMOSの2種類がある。MOSFETが個別にパッケージされたディスクリート部品では4端子が別々に出ているものも少数存在するが、一般的にはソースとバックゲートを内部で直結した3端子になっており、回路図記号はその構造を反映してバックゲートが省略されることもある。

特殊なものとしては、1つのチャネルに複数のゲートがあるマルチゲート(2つならダブルゲート)のFET(マルチゲート素子も参照)や、2つのFETを組み合わせたデュアルFETがある(バイポーラのトランジスタと同様、同一のシリコンチップに作り込んであって特性が揃っている、というものもあれば、単に同一のパッケージ内に2個入っているだけのものもある)。

構造

[編集]高耐圧パワーMOSFETなど特殊なFETの品種を除いて、通常のFETはソースとドレインは対称構造であるため物理的な違いはなく、電流を流す向きにより便宜的にソースとドレインとしている。p型チャネルは高電位側がソース/低電位側がドレイン、n型チャネルは高電位側がドレイン/低電位側がソースとなる。ただし前述のようにディスクリートの3端子のMOSFETはソースとバックゲートが内部で直結されているため、ソースとドレインは逆にできない。

構造上、MOSFETのバックゲートとソースおよびドレインの間にはpn接合があり、寄生ダイオードと呼ぶ。MOSFETの回路図記号の中央に書かれることがある矢印は、この寄生ダイオードの順方向バイアスを示している(横に別に大きく描くこともある)。パワーMOSFETで誘導性負荷やモータを駆動する際、オフ時の過渡的な逆起電力を逃すためのフリーホイールダイオードとして働かせるようにすると有用である。寄生ダイオードを通してバックゲートから電流が流れないようにするため電位がp型チャネルではバックゲート≧ソース≧ドレイン、n型チャネルではドレイン≧ソース≧バックゲートになるように接続する。つまり、ドレイン・ソース間の電流は、矢印と反対方向に流れる。

チャネル

[編集]FETのドレイン・ソース間に流れる電流が通過する領域をチャネルという。半導体にn型とp型が存在するのと同様、チャネルにはn型チャネルとp型チャネルの2種類が存在する。n型チャネルでは負電荷 (negative charge) を帯びた電子が、p型チャネルでは正電荷 (positive charge) を帯びた正孔がキャリアとなる。ゲート電圧によりチャネルに生じる電界がキャリアを集め、もしくは斥けることでキャリア濃度が変化し、したがって抵抗率が変化する。ここで、チャネルの型はFETの動作領域において導電に寄与するキャリアのタイプに基いて決まるものであり、実際のチャネルを構成する半導体のn型・p型と一致しない場合がある点に注意が必要である。実際に、HEMTではチャネル部分の半導体はi型であり、MOSFETでは、n型チャネルの場合、p型の半導体中の反転層を電子が流れることになる。このチャネルの型を示すため、FETのタイプの前にnやpの文字をつけて表すこともある(例えば、NMOS、PMOS)。

なお、一般に使用されるCMOS(相補型MOS、Complemetary MOS の略)は、NMOSとPMOSを組み合わせた構造であることを示し、CMOSと呼ばれるMOSのタイプがあるわけではない。

分類

[編集]ゲート電圧とドレイン電流の関係による分類

[編集]- エンハンスメントモード (enhancement mode) 動作 = ノーマリーオフ (normally off)

- ゲート電圧をかけないときはチャネルが存在せずドレイン電流が流れないもの。入力が電流か電圧かの違いがあるが、バイポーラトランジスタの動作特性に似ている。MOSFETのほとんどはこちら。回路図記号では、縦棒を区切ってノーマリーオフであることを表現する。

- ディプリーションモード (depletion mode) 動作 = ノーマリーオン (normally on)

- ゲート電圧をかけないときもチャネルが存在しドレイン電流が流れるもの。逆電圧(ピンチオフ電圧)が掛かると電流が止まる。真空管の動作特性に似ている。JFETは全てこちら。ディスクリートのMOSFETでは、広く市販されているものでは極く一部の高周波小信号用の品種のみ。また、集積回路技術でCMOSが一般的になる以前に、NMOS方式の一種のdepletion-load NMOSのVdd側に使う、という用法があり、Z80など8ビット時代、ないし16ビット時代の初期のマイクロプロセッサのいくつかのオリジナル版はそれのことがある。

- ゼロスレッショルド

- 以上の2種類の動作のちょうど中間で、ほぼ0V付近に閾値電圧があるように製造時に調整されたMOSFET。閾値電圧は製造バラツキが比較的大きいため、従来はそのような市販製品は無かったが、近年の技術開発により市販されるようになった。

ゲート接合部の構造による分類

[編集]- MOSFET(MOS = Metal-Oxide-Semiconductor、金属-酸化物-半導体)

- ゲート金属電極の下の半導体部分表面が酸化膜による絶縁膜になっている。現在の集積回路の主流となっている。特にP/N両型を相補的に利用するCMOS型が多用されている。

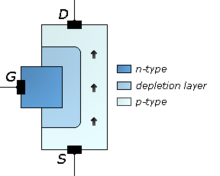

- 接合形(Junction FET, JFET)

- ゲート部分がpn接合になっている。

- 金属半導体形(Metal Semiconductor FET, MESFET)

- ゲート部分が金属電極と半導体の直接接合(ショットキー接合)になっているもの。

n型チャネル接合型FETのモデル

[編集]

(MOSFETについてはそちらの記事を参照のこと)

接合型 FET は通常ゲート端子がドレイン・ソース両端子よりも低い電圧で用いる。このときゲート端子は高インピーダンスでほとんど電流を流さない。よって考えるべき電流はドレインからソースへ流れる電流 iDS のみである。 ソース電圧を基準に取り、ゲート電圧を vGS (≤ 0)、ドレイン電圧を vDS と表せば、iDS はこれらの関数としてモデル化される。 ただし以下では vDS ≥ 0 とする。

この関数は、定義域をオーム領域(ohmic region, または線型領域)、飽和領域 (saturation region)、ピンチオフ領域 (pinch-off region) という3つの領域に分割する。ピンチオフ領域はゲート電圧がピンチオフ電圧 (pinch-off voltage) Vp とよばれる負の決まった電圧以下の領域である。この領域では電界によりチャネルにキャリアが存在しなくなり(空乏層)、ドレイン–ソース間に電流は流れない。すなわち、

である。 ピンチオフ電圧は FET の種類により異なるがおよそ Vp ≈ −3 V とされる。

飽和領域は、ゲート電圧がピンチオフ電圧よりも大きく、かつドレイン電圧がピンチオフ電圧からみたゲート電圧よりも大きな領域であり、ここでは実質的にドレイン–ソース電流はゲート電圧のみの関数である。すなわち、電流はドレイン電圧によらず一定である。ゲート電圧に関してはピンチオフ電圧から測って理想的には 2 乗の特性をもち、式では、

と表される。ただし、IDSS はドレイン飽和電流 (drain saturation current) とよばれる正の電流値で vGS = 0 であるときに流れるドレイン–ソース電流に相当する。このドレイン飽和電流は種類によっても個々の FET によってもかなりのばらつきがある。

これに対して、残りのオーム領域ではドレイン電圧が一定であればドレイン–ソース電流はゲート電圧とともに 1 次でしか増加しない。 一方、ドレイン電圧に関してはそれが 0 のときドレイン–ソース電流が 0 となり、ドレイン電圧とともに上に凸の 2 次曲線を描いて非線型で増加する。モデル上は飽和領域でのゲート電圧の上昇に関する電流の増加と、オーム領域でのドレイン電圧の減少に関する電流の減少は、符号を逆にして 2 乗のオーダーでまったく同じである。すなわち、

となる。

飽和領域は主として増幅用途に用いられるが、オーム領域は特に電圧制御抵抗 (voltage-controlled resistor) として用いることができる。 すなわち、このモデルの特性に基づけば、ゲート端子とゲート端子への入力 x、およびゲート端子とドレイン端子間に同じ大きさの抵抗をつなぎ、ゲート電圧を入力とドレイン電圧とのちょうど中間の電圧 vGS = (x + vDS) / 2 とすることによって、オーム領域での特性を線型化でき、次のように電圧の積に比例した電流を得ることができる。

- (オーム領域)

ただしこれは vDS ≥ 0 のオーム領域でのみ成立する補正であることに注意する必要がある。

用途

[編集]電界効果トランジスタ(FET)はその電気的特性から、スイッチング素子や増幅素子として利用される。特にMOSFETでは消費電力を小さくできることに加え、構造が平面的であるため、バイポーラトランジスタと比較して製造や集積化が容易である。そのため集積回路では必要不可欠な素子となっている。デジタル回路では論理回路の基本素子として演算処理装置、記憶素子として使用され、アナログ回路では無線LAN等に代表される通信分野のトランシーバーにおいて、送受信に使用される各種回路(LNA、フィルタ、ミキサ等)として使用され、アナログスイッチや電子ボリュームなどにも応用される。極超短波以上ではシリコンよりもキャリアの移動度が高いヒ化ガリウム (GaAs) のような化合物半導体などを用いた電界効果トランジスタ(FET)が用いられている。

この他、接合型FETには電気的特性が真空管にかなり近いという特徴があるため、初期の接合型FETには、小型化に逆行してあえて真空管と同じサイズと形状のパッケージを採用して、真空管を使った回路の設計変更を回避するという使用法があった。

定電流ダイオードとして

[編集]電界効果トランジスタ(FET)の飽和領域動作では「ゲート電圧が一定であればドレイン電流が一定」であるため、回路に直列に接続してある程度以上の電圧が加わるようにしておけば、常に一定の電流が流れる定電流素子として使うことができる。これを利用する、JFETのゲートをソースと直結し2端子化して定電流ダイオードと称した部品がある。順方向の使用で定電流の性能を発揮し、発光ダイオードの電流制限などに利用されている。ダイオードの名で、パッケージもダイオードと同じものを使っているが、本来のダイオードとは構造は全く異なり,逆方向の電流を制限する整流作用もない。

参考文献

[編集]- 最新FET(電界効果トランジスタ)規格表 各年度版(CQ出版社) - 1968年版(初版)から1986年版までは個別特性図が付いていた。1987年版から個別特性図ははずされた。1994年版から初期のFETの規格が外された。

- S. M. Sze, (1985). Semiconductor devices, physics and technology. New York: John Wiley & Sons

- S.M.ジィー『半導体デバイス―基礎理論とプロセス技術』(第2版)産業図書、2004年。ISBN 4782855508。