強誘電体メモリ

この記事は英語版の対応するページを翻訳することにより充実させることができます。(2024年5月) 翻訳前に重要な指示を読むには右にある[表示]をクリックしてください。

|

(きょうゆうでんたいめもり、英: ferroelectric random access memory)とは、FeRAMとも呼ばれる、強誘電体のヒステリシス(履歴効果)に因る正負の残留分極(自発分極)をデジタルデータの1と0に対応させた不揮発性メモリのことである。なお、FRAMは同種のRAMのラムトロン・インターナショナル(現・サイプレス・セミコンダクター[1])による商標で、日本では富士通が同社とのライセンスによりFRAMの名称を使用していた[2]。

強誘電体膜の分極反転時間は1ns以下であり、FeRAMはDRAM並みの高速動作が期待される。

構造と動作原理

[編集]FeRAMのセルにはキャパシターが用いられており、この意味においては、DRAMと基本的に類似したセルである。しかし、このキャパシターの極板間の材料には強誘電体が用いられているという点で、FeRAMはDRAMとは大きく異なる。

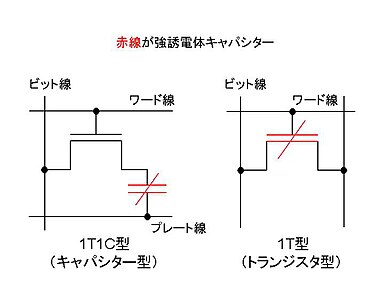

メモリセル[注釈 1]構成としては、FeRAMには大きく分けて2種類が提案されている。具体的には、強誘電体キャパシター(C)とメモリセル[注釈 1]選択用のMOSFET(T)を組み合わせる1T1C型(キャパシター型)と、これをベースにして2つのキャパシターを逆向きに分極させることでデータの信頼性を高めている2T2C型である。なお、1T1C型はDRAMと同じメモリセル[注釈 1]構成でもある。

更に、この他に、ゲート絶縁膜が強誘電体から成るMFS-FET又はMFMIS-FETを用いる1T型(トランジスター型)が存在し、これは特にFFRAMと呼ばれて区別されている。

FeRAMでは、FETをオンさせただけではビット線にはデータは出力されない。何故ならば、セルであるキャパシターに電圧が印加されない状態では、セルに記憶されているデータが1であるか0であるかは強誘電体膜中に保存されているので、それを読み出すにはソースプレートを駆動してキャパシターに電圧を印加して強誘電体膜中の分極を外部に電荷量として読み出さなければならないからである(これは読み出しに静電容量が極めて大きいセルキャパシターを駆動する時間を必要とすることも意味する。)。従って、FeRAMにおいては、ワード線とビット線以外にも、ソースプレートの駆動線と特定のセルのそれを駆動するためのデコーダー回路が必要となる。

このためFeRAMでは、セルの微細化やアクセス速度の高速化は困難であった。これらの欠点を克服すべく、東芝がChainFeRAMと呼ばれる新しいメモリセル[注釈 1]構造のFeRAMを2001年に発表している[3][注釈 2]。

- FeRAMのメモリセル

-

1T1C型及び1T型(最も基本的な構成)

-

2T2C型

-

2T2C型のタイミングチャート

1T1C型

[編集]書き込み時にはワード線でセルである強誘電体キャパシターを選択し、ビット線とソースプレートの間に電圧を印加して強誘電体膜を分極させる。読み出し時にはパルス電圧を加えて分極反転による電流が流れたかどうかでセルに蓄えられたデータをセンスアンプで判定する。この時、分極は元の状態に依らずに電圧印加方向を向く(同方向ならば電流が流れず、反対方向ならば分極反転して電流が生じる。)ので、破壊読出しとなる。このため、読み出す時には必ず再書き込みを必要とするので、書き込み回数に読み出し回数も含まれる。

キャパシター膜が常誘電体でなく強誘電体であるので、FETにリーク電流が有ったり電源が遮断されてもキャパシターの電荷を失わない(データが消えない)。つまり、不揮発メモリであると同時にリフレッシュが不要であるため、消費電力が少ない。

2T2C型

[編集]1T1C型と同様にワード線に拠ってセルの強誘電体キャパシター1を選択する。書き込みは同様にソースプレートの昇圧によっが、この時に、対となっている強誘電体キャパシター2の電界効果トランジスタのビット線にも時間差を付けて昇圧する。このままではソースプレートを降圧した時点で対となっている側の強誘電体キャパシター2には負の電圧が印加されるため、書き込みを意図している強誘電体キャパシター1とは逆方向に残留分極が発生する。こうして互いに異なる向きの分極が形成されるため、「0・1」または「1・0」という組み合わせでデータを表す。

読み出し時も同様にワード線とソースプレートを昇圧して、ビット線のどちらの電圧の変化が大きいか(どちらに変位電流が流れるか)を測定することでデータを判定する。なお、この時に順方向の分極を持つ強誘電体キャパシター1でも電圧が変化するのは分極の微小変位によるものである。また、読み出し時に、強誘電体キャパシター2のワード線より先にソースプレートを降圧すると、負の電圧が印加されて再書き込みが行なわれ、読み出し時のデータ破壊を防げる。

強誘電体膜の材料

[編集]FeRAMに用いられる強誘電体膜の材料には以下のような性質が要求される。

- 大きい残留分極

- 小さなキャパシター面積で大きな分極反転電流を実現してメモリセル[注釈 1]アレイ部分の回路レイアウトにおいて高密度化を実現できる

- 低い比誘電率

- 分極反転しない場合の変位電流を低減して読み出しエラーを避けられる

- 低い抗電界

- 低電圧駆動に拠る省電力化

- 小さいリーク電流

- 電源を切っても室温で10年間以上に亘る残留分極(データ)保持(リテンション[注釈 3])特性

- 小さい分極反転疲労(ファティーグ)[注釈 4]特性

- 10年程度の動作保証性を実現するための目安として1012回(理想的には1015回)以上の分極反転に耐えられる

- 小さいインプリント(刷り込み)[注釈 5]特性

- 書き込みエラーを減らせる

なお、インプリント[注釈 5]や分極反転疲労[注釈 4]及びリーク電流は強誘電体膜内部の結晶粒界や結晶欠陥に起因する。

上記の条件を満たす材料として、下記の様な、従来の半導体製造プロセスでは使用されていないセラミック材料が存在する。これらの多くの強誘電体材料では、分極が容易な軸の方向に沿った異なる2つの分極状態を利用してデータの書き込みや読み出しを行っている。言い換えれば、強誘電体結晶の多くは、結晶の対称性によってその分極状態の数は限られている。

PLZT

[編集](Pb,La)(Zr,Ti)O3

- 他の分野での実用化が進んでおり、成膜方法のノウハウが蓄積されている。

- 残留分極量が、配向に依存して25μC/cm2から100μC/cm2と大きく、高密度化に適している。

- 結晶化温度が550℃と低く、集積回路の半導体製造プロセスと相性が良い。

- 人体に有害な鉛が含まれているため、環境基準に対応できない。

- 高温処理に耐えられる白金や金などを電極に用いると疲労現象[注釈 4]が著しくなり、107回以下の分極反転で残留分極が顕著に減少する。ただし、IrO2などの電極材料を用いた場合は1012回以上の分極反転にも耐えられる。

本材料系では、従前、分極ドメインのナノ構造化に拠って分極が容易な軸の方向が結晶の対称性に束縛されず極軸が自由に回転することが既に示されている。これは記録密度が従来に対して2桁増大するという可能性を示している。 そして、2014年に、その分極自由回転状態の書き込みと読み込みの実証が報告されている[4][5][6]。

SBT

[編集]- 抗電界が、PZTの60kV/cmなどよりも、40kV/cmと小さく、低電圧駆動させられる。

- 電極材料に依らず、高い疲労[注釈 4]耐性を持ち、1012回以上の分極反転に耐えられる。

- インプリント現象[注釈 5]が起き難い。

- 強誘電性を得るためには700℃以上の高温で結晶化させねばならない。

- 残留分極を持つa軸方向に薄膜を成長させ難い。

- 残留分極量が25μC/cm2と相対的に小さい。

BLT

[編集](Bi,Ln)4Ti3O12 Ln=La, Nd, Pr, etc.

- 残留分極量が配向に依存して10μC/cm2から50μC/cm2と比較的大きい。

- Biに対してLaを10%から20%程度添加すると、疲労現象[注釈 4]を抑制できる[7][8]。

- 600℃という低温で形成できる[9]

- 配向を制御して結晶化させ難いため、現状では残留分極量が小さく抗電界が高い。

実用

[編集]世界で初めてFeRAMを実用化したのはレイコム・システムズである。それは256ビット品で非接触ICカードでの利用をターゲットとして開発された。

FeRAMは、従来広く用いられてきたEEPROMよりも、動作が高速で消費電力が低く、セルサイズも15F2と小さく[注釈 6]、フォトマスクの追加が少なくて済むなど半導体製造プロセスとの相性も良い。このため、2006年に富士通のFRAMがソニーのFelicaに採用され[10]るなど、少なくとも日本においては、既に一般生活において身近に普及している。

ただし、パーソナルコンピュータなどに搭載される主記憶装置の代替としては未だに実用化の目途は立っていない。

関連項目

[編集]- ユニバーサル・メモリ

- 強誘電体メモリ(FeRAM or FRAM)

- 強誘電体浮遊ゲートメモリ(FFRAM)

- 強誘電体メモリ(FeRAM or FRAM)

- 法人

- 環境基準

脚注

[編集]注釈

[編集]出典

[編集]- ^ “Cypress Semiconductor has acquired Ramtron International Corporation” (英語). 2014年3月7日閲覧。

- ^ “強誘電体メモリ「FeRAM」への呼称変更のお知らせ” (2022年6月28日). 2024年3月3日閲覧。

- ^ 「新不揮発性メモリChainFeRAM」(PDF)『東芝レビュー』第56巻第1号、東芝、2001年1月、51-54頁。

- ^ “Deterministic arbitrary switching of polarization in a ferroelectric thin film”. Nature Communications 5 (Nature Publishing Group) (4971). (2014-09-18). doi:10.1038/ncomms5971.

- ^ 『強誘電体メモリー、超高密度化に道』(PDF)(プレスリリース)東北大学、2014年9月19日。

- ^ “東北大、強誘電体メモリの記録密度を大幅に向上させる可能性を示す”. マイナビ. (2014年9月22日)

- ^ “Direct observation of oxygen stabilization in layered ferroelectric Bi3.25La0.75Ti3O12” (PDF). APPLIED PHYSICS LETTERS (American Institute of Physics) 91 (062913). (2007-09-10). doi:10.1063/1.2768906.

- ^ (PDF) Direct observation of oxygen stabilization in layered ferroelectric Bi3.25La0.75Ti3O12. 理化学研究所. (2007-09-10).

- ^ 『FeRAM用新強誘電体薄膜の低温成膜に成功』(プレスリリース)富士通、2001年3月30日。

- ^ 『FRAM搭載LSIがFeliCa方式ICカードに採用』(プレスリリース)富士通、2006年11月7日。

参考資料

[編集]- 石原宏 編『強誘電体メモリーの新展開』シーエムシー出版、2004年2月。ISBN 978-4-88231-819-4。

- 田中均洋・三浦薫・磯辺千春 訳『強誘電体メモリ 物理から応用まで』シュプリンガー・フェアラーク東京、2003年11月1日。ISBN 978-4-43171-057-8。

- 塩嵜忠・宮坂洋一・望月博・崎山恵三 編『強誘電体メモリ先端プロセス』サイエンスフォーラム、1999年9月13日。ISBN 978-4-916-16431-5。

- 塩嵜忠・阿部東彦・武田英次・津屋英樹 編『強誘電体薄膜メモリ』サイエンスフォーラム、1995年6月。

- 高須秀視・宅間俊則 編『FRAM ICカード技術』サイエンスフォーラム、1999年4月。

- 塩嵜忠・阿部東彦・崎山恵三 編『強誘電体薄膜集積化技術』サイエンスフォーラム、1992年2月。

- “FRAMとは”. 富士通. 2014年10月1日閲覧。

- “FRAMの品質・信頼性保証”. 富士通. 2014年10月1日閲覧。

- “AD00-00015-4.pdf” (PDF). 富士通セミコンダクター. 2014年10月1日閲覧。

- 小柳光正 編『次世代半導体メモリの最新技術』シーエムシー出版、2009年2月。ISBN 978-4-88231-992-4。

- 小柳光正 編『次世代半導体メモリの最新技術』(普及版)シーエムシー出版、2013年9月6日。ISBN 978-4-7813-0735-0。

- 堀内かほり. “次世代不揮発性メモリー 風変わりな記憶素子を使い高速・低消費電力を目指す (上)”. ITpro. 日経BP. 2003年10月8日閲覧。

- 堀内かほり. “次世代不揮発性メモリー 風変わりな記憶素子を使い高速・低消費電力を目指す (中)”. ITpro. 日経BP. 2003年10月8日閲覧。

- 堀内かほり. “次世代不揮発性メモリー 風変わりな記憶素子を使い高速・低消費電力を目指す (下)”. ITpro. 日経BP. 2003年10月9日閲覧。