ウルトラRAM

この項目は内容が専門的であり、一般の閲覧者にはわかりにくくなっているおそれがあります。 |

ウルトラRAM(英: UltraRAM)はブランド名および開発中のストレージ・デバイス技術である。ランカスター大学物理学部および工学部がウォーリック大学物理学部との協力により不揮発性メモリ技術における改善を提唱する論文[1]をAdvanced Electronic Materials 誌に共同発表した。それはハード(ディスク)ドライブのようにデータを保持できること意味する「(フラッシュのような)データストレージ・メモリーの不揮発性と(DRAMのような)速さ、エネルギー効率、そしてワーキングメモリーの耐久性の組み合わせる」メモリー・ストレージ技術として言及されている[2]。ランカスター(大)チームが作動原理をデモするために実際にいくつかの基礎実験を披露する一方で、ウルトラRAMは現時点では大概相変わらず理論上(の存在)に留まっている[3]。ランカスター大の研究者いわく、「品質を改善し、製造プロセスを微調整し、そしてウルトラRAMデバイスを実装およびスケールするためのさらなる作業が進行中である」とのこと[4]。

歴史

[編集]2023年にウルトラRAMをさらに開発するためにQuInAsカンパニーが設立された[5]。

メモリのコンセプト

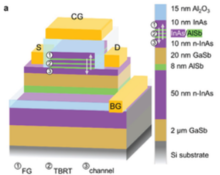

[編集]ウルトラRAMはチャージ(充電)ベースのメモリであり、そこでは論理状態がFG(浮遊ゲート)での電子の有無によって決定される。FGはAl2O3絶縁体によって制御ゲート(CG)から、そしてInAs / AlSb TBRTヘテロ構造から成る配下のチャネルからも電気的に分離される。

FGにおける電子の充足((NANDフラッシュみたく)真偽値0を定義する[6])は配下にあるn型InAsチャネルにてキャリアを使い果たし、その伝導率を減らす。結果、FGの充電状態および(それゆえに) メモリの論理状態は、ソース(S)とドレン(D)の接点の間に電圧が印加されたときチャネルを通過する電流を計測する事によって非破壊的に読み出される。メモリの最後のコンポーネントは種々の操作のためにゲート・スタックに渡って電圧を垂直方向に印加することを可能にするInAsバック=ゲート(BG)である。

本メモリを支える目新しさはTBRT (トリプル・バリア共鳴トンネル) 構造であり、それは(単層バリアとは異なり)たった±2.5Vの印加により電気的高抵抗性状態から高伝導性状態に切り替えられることにある。これはAlSbバリアとInAs QW(量子井戸)層の厚さを注意深く設計することによって実現される。メモリが保持状態にあるとき(すなわち)デバイスに電圧が印加されていない場合、TBRT QWにおける電子基底状態は互いにずれており、 そして、それはInAs FGとチャネル層の電子密度をエネルギー的に300K以上はるかに上回っている。実際、不揮発性は共鳴トンネル構造のために異常に高いエネルギーで存在するQWの基底状態によって強化される。これは極薄QWsとInAsにおける非常に低い電子有効質量との組み合わせによるものである。この状態では、TBRTはFGに出入りする電子移動を妨げる巨大なバリアを提供する。しかしながら、デバイス全体に適切なバイアスを印加することは、(プログラム操作中の)チャネルもしくは(消去操作中の)FGにおける電子状態に従事し協調するTBRT QWの基底状態のような伝導帯を傾ける。これはTBRT領域を横切って共鳴トンネリングの本質的に高速な量子力学的プロセスによって意図した方向に迅速に電子が移動することを可能にする。DRAMと比して低電圧しか要しないのとデバイスの単位面積あたりの静電容量が低いため、10−17 Jの超低論理状態切り替えエネルギーが20nm平面図法サイズのウルトラRAMメモリについては予測されており、これはDRAMとフラッシュよりもそれぞれ2桁と3桁の低さである。しかしながら、この超低切り替えエネルギーはnmスケール・デバイスを製造することによって実現できる前に、μmスケール・デバイスの基礎的物性を最初に理解し最適化する必要がある。GaAsサブストレートで成長させたウルトラRAMの試作品は以前、105秒の不揮発性保持および106回のプログラム=消去サイクルの実験限界(デバイス(の寿命)限界ではない)を明示していた[1]。

動作(原理)

[編集]

充電されたFGは真偽値「0」として、そして充電切れは真偽値「1」として定義される。プログラムと消去サイクル(それぞれがFGの充電と放電である)はCGで±2.55V以内(≤)の電圧パルスを使用する。

サブμm平面図法サイズのInAsチャネル・トランジスタおよび100 mV/dec未満のサブスレッショルド変動(subthreshold swing)が以前に実証されている[7]。したがって、ランカスター(大)チームが設計したデバイスの閾値電圧窓が350mVであるため、ノーマリー=オフ・チャネルの実装に伴い(真偽値)0/1しかないウルトラRAMの電流比を3ディケード倍に改善することが期待される。チャネルの注意深い修正を通じた0/1比のそのような改善は、メモリアレイを奇抜な高密度RAMアーキテクチャにより構築されることを可能にするだろう[1]。

大義

[編集]シリコン・デバイスにおけるウルトラRAMは実際に以前の技術の権化であるGaAs化合物半導体ウェハー上でアウトパフォームしており、少なくとも(推定)1000年間のデータ保管時間、(デバイスサイズにおいて)高速スイッチング速度を、そして(フラッシュよりも100〜1000倍優れている)少なくとも1000万(回)のプログラム=消去サイクリングの耐久性を実証している。この作業を主導しているランカスター大学物理学部のManus Hayne教授いわく、「シリコン上のウルトラRAMは我々の研究にとっては大いなる前進であり、大きな結晶格子の不一致という超重要な材料の課題および、元素から化合物半導体への変化および(それに伴う)熱収縮の違いという課題を克服する。」[2]と言った。

称賛

[編集]2023年8月11日、それ(QuInAs)は第17回フラッシュメモリ・サミット(FMS '23)で「最(優秀)革新的フラッシュメモリ・スタートアップ」賞に勝った[8]。

関連項目

[編集]脚注

[編集]- ^ a b c Hodgson, Peter D.; Lane, Dominic; Carrington, Peter J.; Delli, Evangelia; Beanland, Richard; Hayne, Manus (2022-01-05). “ULTRARAM: A Low-Energy, High-Endurance, Compound-Semiconductor Memory on Silicon” (英語). Advanced Electronic Materials 8 (4): 2101103. doi:10.1002/aelm.202101103. ISSN 2199-160X.

- ^ a b “Mass production of revolutionary computer memory moves closer with ULTRARAM on silicon wafers for the first time” (英語). ScienceDaily. 2022年4月8日閲覧。

- ^ “'UltraRAM' breakthrough could merge storage and RAM into one component” (英語). PCWorld. 2022年4月8日閲覧。

- ^ “UltraRAM Breakthrough Brings New Memory and Storage Tech to Silicon” (英語). Tom's Hardware (2022年1月10日). 2022年4月8日閲覧。

- ^ “UltraRAM Demos Prototype Chip, Secures Funding to Validate Commercial Potential” (英語). Tom's Hardware (2023年9月26日). 2023年9月26日閲覧。

- ^ (日本語) 光る太陽と記憶するフラッシュメモリ 2024年3月1日閲覧。

- ^ Chang, S. W.; Li, Xu; Oxland, R.; Wang, S. W.; Wang, C. H.; Contreras-Guerrero, R.; Bhuwalka, K. K.; Doornbos, G. et al. (30 January 2014). “InAs N-MOSFETs with record performance of Ion = 600 μA/μm at Ioff = 100 nA/μm (Vd = 0.5 V)”. 2013 IEEE International Electron Devices Meeting. pp. 16.1.1–16.1.4. doi:10.1109/IEDM.2013.6724639. ISBN 978-1-4799-2306-9

- ^ “Flash Memory Summit Announces 2023 Best of Show Award Winners”. kalkinemedia.com (2023年8月12日). 2023年9月28日閲覧。

外部リンク

[編集]- Nasser, Hussein (19 Jan 2022). “Is ULTRARAM a game changer?”. YouTube. Template:Cite webの呼び出しエラー:引数 accessdate は必須です。

- Promotion video: https://www.youtube.com/watch?v=iz-sYyfojw4