利用者:加藤勝憲/パイプライン・ストール

パイプライン・ストール(英: Pipeline stall)とは、プロセッサのパイプライン命令設計において、ハザードを解決するために命令の実行が遅延することである[1]。

In the design of pipelined computer processors, a pipeline stall is a delay in execution of an instruction in order to resolve a hazard.

詳細

[編集]標準的な5段パイプラインでは、デコード段階で、制御ユニットは、デコードされた命令が、現在実行されている命令が書き込んでいるレジスタから読み出すかどうかを判断する。 この条件が成立する場合、制御ユニットは命令を1クロックサイクルストールさせる。 また、フェッチ段階の命令がプログラムの次の命令によって上書きされるのを防ぐために、フェッチ段階の命令をストールする[2]。

プログラム・カウンタ(PC)レジスタを使用してパイプラインでフェッチされている現在の命令を決定するフォン・ノイマン方式では、デコード段の命令がストールしたときに新しい命令がフェッチされないように、PCレジスタの値とフェッチ段の命令が変更されないように保存される。この値は、競合の原因となった命令が実行ステージを通過するまで保持される[3]。このような現象は、流体パイプ内の気泡になぞらえて、しばしばバブルと呼ばれる。

あるアーキテクチャでは、パイプラインの実行ステージは、サイクルごとに常にアクションを実行しなければならない。 その場合、バブルはNOP("no operation")命令を実行ステージに送り、バブルが実行ステージを通過してフラッシュされるまで実装される。

事例

[編集]タイムライン

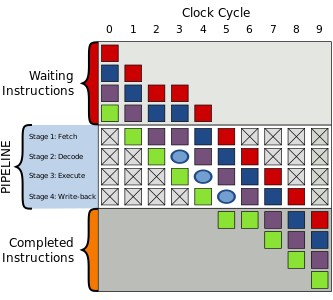

[編集]以下は、同じ4命令を4段パイプラインで2回実行したものだが、何らかの理由で、2サイクル目の紫命令のフェッチが遅れたためにバブルが発生し、それ以降の命令もすべて遅延している。

|

|

| 通常の実行 | Execution with a bubble |

Classic RISC pipeline

[編集]以下の例は、5つのステージ(IF=命令フェッチ、ID=命令デコード、EX=実行、MEM=メモリ・アクセス、WB=レジスタ・ライトバック)を持つ古典的なRISCパイプラインにバブルが挿入される様子を示している。 この例では、第1命令のMEMステージ(第4ステージ)の後に利用可能なデータが、第2命令のEXステージ(第3ステージ)の入力として必要となる。 バブルがなければ、EXステージ(第3ステージ)は前のEXステージの出力にしかアクセスできない。 したがって、バブルを追加することで、データを時間的に逆伝播することなく(不可能であるが)、時間依存性を解決することができる。

| Bypassing backwards in time | Problem resolved using a bubble |

|

|

関連項目

[編集]- Branch predication

- Delay slot

- Pipeline flush

- Wait state

脚注・参考文献

[編集]- ^ Patterson, David A.; Hennessy, John L., Computer Organization and Design (4 ed.), Morgan Kaufmann, p. 338

- ^ Patterson, David A; Hennessy, John L (2014) (英語), Computer organization and design: the hardware/software interface (5th ed.), pp. 318, OCLC 1130276006 2020年5月25日閲覧。

- ^ Patterson, David A.; Hennessy, John L., Computer Organization and Design (4 ed.), Morgan Kaufmann, p. 373

[[Category:命令処理]]