マルチコア

マルチコア (英: multiple core, multi-core) は、1つのプロセッサ・パッケージ内に複数のプロセッサ・コアを搭載する技術であり、マルチプロセッシングの一形態である。

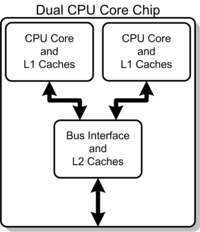

外見的には1つのプロセッサでありながら論理的には複数のプロセッサとして認識されるため、同じコア数のマルチプロセッサと比較して実装面積としては省スペースであり、プロセッサコア間の通信を高速化することも可能である。主に並列処理を行わせる環境下では、プロセッサ・チップ全体での処理能力を上げ性能向上を果たすが、アムダールの法則による制約を受ける。このプロセッサ・パッケージ内のプロセッサ・コアが2つであればデュアルコア (dual-core)、3つであればトリプルコア (triple-core)、4つであればクアッドコア (quad-core)、6つであればヘキサコア (hexa-core)、8つは伝統的にインテルではオクタルコア (octal-core)、AMDではオクタコア (octa-core) と呼ばれるほか、オクトコア (octo-core) とも呼ばれる。さらに高性能な専用プロセッサの中には十個以上ものコアを持つものがあり、メニーコア (many-core) と呼ばれる[1]。

なお、従来の1つのコアを持つプロセッサはマルチコアに対してシングルコア (single-core) とも呼ばれる。

概要

[編集]マルチコアはシングルコアに対し、プロセスルールが同じであれば、実装したプロセッサ・コア数に比例してダイが大きくなる。面積が増えると、級数的に製造不良が増えるなど製造の面での難度が上る(歩留まりが悪化する)。

並列コンピューティングに対応したプログラミングが必要なため、ソフトウェアの開発は難しくなるが、OSやミドルウェアなどが並列処理の支援を行なうことでソフトウェア開発は容易なものとなる場合がある。既にマルチプロセッサ対応しているシングルコア・プロセッサを基にする、マルチコア・プロセッサの製品化は論理設計を省略できるため比較的簡単である。

性能が要求されるワークステーション、サーバ分野はもとより、パーソナルコンピュータ (PC) でも、高消費電力と廃熱処理(および冷却に伴う騒音対策)などによる制約や、クロック周波数向上対効果の停滞などにより、この技術へのシフトが進んでいる。

マルチコア・プロセッサは消費電力低減と発熱抑制を目的に、各コアごとに動作電圧やクロック・スピードの可変制御を行なったり、休止状態を含む動作状態の制御を行なっている製品もある。コアごとに複数の電圧で給電するシステムが別途必要となるため、単一電圧に比して設計・実装・製造難易度は高い。

マルチコア・プロセッサに似た技術に、同時マルチスレッディング (simultaneous multi-threading, SMT) がある。これは1つのプロセッサを外部から2つ以上に見せるという点では同じだが、実際に存在しているコアは1つ、すなわちシングルコアであるという点でマルチコア技術とは根本的に異なる。

用語

[編集]効果的に説明するために、まず使用する用語を示す。

- ダイ (die)

- シリコンウェハー上に半導体回路を作り、四角に切り出したもの。ベア・チップやペレットとも呼ばれる。ダイはプロセッサ・パッケージ(CPUパッケージ)と呼ばれる覆いで封止されている。プロセッサはパッケージ化によって、基板との接点、ヒートスプレッダ、コンデンサ、抵抗などが一体となっている。

- 半導体産業ではプロセス済みのウェハーやダイの生産までが上流工程であり、テストとパッケージ封入が下流工程になる。大手半導体企業で自社生産としている場合でも下流工程はアウトソーシングしていることがある。シリコンウェハーは無塵環境で製造されるが、不純物等の影響で不良箇所の発生が避けられない。ダイ上のどこか一箇所にでも不良があれば製品にはならないため、プロセスルールの微細化による回路の縮小でダイサイズを縮小し、シリコンウェハーからの切り出しを細分化して数を増やせば、ウェハー生産数に対するダイ不良品の数を減らすことができ、利益率が上がる。

-

AMD 486 DX 2 66 MHzのパッケージ裏面のカバーを外した様子。中央の黒と緑の部分がダイ。

- コア (core)

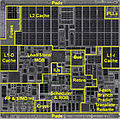

- コアとは、プロセッサ・ダイ上に作成されるプロセッサ回路の中核部分で、「キャッシュメモリ」を除く半導体回路部分。ただし、他のコアとは共有しない、コアごとのキャッシュメモリはコアに含める事がある。多くの場合、プロセッサ・ダイはコア、キャッシュメモリ、ボンディング・パッド等の接続部から構成される。

-

VIA Isaiahのダイの構成。おおまかに、上半分がキャッシュで下半分にコアが配置されている様子がわかる。

-

Quad-Core AMD Opteronのダイ。Quad-Coreでホモジニアスマルチコアなので、おなじパターンの回路が4つある。

- サブストレート (substrate)

- ダイを載せて外部接続ピンなどの外力から守るデジタル半導体の主要構成部材の1つ。MCM (Multi-Chip Module) やMCP (Multi-Chip Package) の場合には1つのサブストレートに複数のダイが載る。

- チップ (chip)

- いくぶん不明瞭な意味で、半導体部品を意味する。ダイやペレットを指す場合もある。また、表面実装技術 (surface mount technology, SMT) の受動部品を指す場合もある。

背景

[編集]ポラックの法則では、プロセッサを構成するトランジスタ数をプロセス微細化を行なわずに単純に2倍にした場合、ダイサイズは2倍となるが、処理能力は倍(約1.4倍)にとどまるとされている。一方で、消費電力はトランジスタ数に比例する。この法則によれば2倍のコストで1.4倍のリターンしか得られず、プロセッサあたりのトランジスタ数を増やすことは非効率となる。

にもかかわらずn倍のトランジスタを使ってnコアのプロセッサを実装するのは、シングルコアでは壁があるからだ、ということが単純には言える。

以下ではメインフレームやスーパーコンピュータのマルチプロセッサ化や、それを1チップに集積したマルチコア化の歴史は略史としミニコンピュータとワークステーションについては割愛。マイクロプロセッサのマルチプロセッサ化や、そのパーソナルコンピュータでの実現について、背景から述べる。

マルチプロセッサ

[編集]メインフレームでは、UNIVAC 1108(1964年)[2]が最初期のマルチプロセッサシステムとして知られる。IBMのSystem/360(1964年)はモデル65・67で(en:IBM System/360 Model 65・en:IBM System/360 Model 67)で、マルチプロセッサ化が可能となった。

富士通・日立では、FACOMはFACOM230-60(1968年)がマルチプロセッサ機であり[3][4]提携しているアムダールも1980年代にはマルチプロセッサ化した。HITACはHITAC 8800/8700(1970年・1971年)がマルチプロセッサ機であり[5][6]両社ともに引き続くMシリーズではその初期よりマルチプロセッサ化した(FACOM Mシリーズ・HITAC Mシリーズ)。

日本電気・東芝はTOSBAC-5600(1970年)[7][8]と、それを踏襲したACOSシリーズ77 システム600, 700[9](1974年、ACOS-6系)からマルチプロセッサ化した。

クレイのスーパーコンピュータでは、Cray X-MP(1982年)が、日本電気のSXシリーズではSX-3(1989年、NEC SX#SX-3)が[10][11]、富士通ではVPPシリーズ(1992年〜)が[12][13]、日立ではHITAC S-3000シリーズ(1992年、en:HITAC S-3000)が[14][15]マルチプロセッサ化のはじまりである。

以上のメインフレームやスーパーコンピュータのマルチプロセッサ化では、最初は個別部品で実装されていたものが、やがてIC化し、LSIによってプロセッサが1チップ化し、という集積度向上の自然な流れとして、1チップにマルチコアが集積されるようになっていった。

マイクロプロセッサの並列使用

[編集]1970年代にマイクロプロセッサが誕生し大量生産されるようになると、そのコストパフォーマンス等の特性から、複数個を束ねて使うというアイディアが生まれた。1977年に始まるPACSプロジェクトでは当初から、パーソナルコンピュータやワークステーションでCPUとして使われるようなマイクロプロセッサを多数並列使用している。またコンピュータグラフィックス用の専用計算機であるが、1982年のLINKS-1もそのようなシステムである[16](発展型のLINKS-2ではカスタムチップでの実装となった[17]。参考: Personal LINKS#歴史)。パーソナルコンピュータが普及すると、その拡張カードに、多数のマイクロプロセッサを搭載して並列処理に利用する、という拡張カードがあらわれ、1995年にはその自作を指南する『つくる並列処理コンピュータ PC-9800シリーズではしる』という書籍が上梓されている[18]。

以上のマイクロプロセッサベースのマルチプロセッサシステムはいずれも、既存のOSを並列プロセッサで実行できたり、既存のアプリケーションをソースコードの小修正で利用できたり、ということはできない、既存システムとは連続性の無いシステムである。

PCアーキテクチャでのマルチプロセッサ化

[編集]ここからは、既存システムと連続性のあるシステムに主眼をおく。

前節で述べたような連続性の無いシステムの延長にあるマルチプロセッサのマザーボードもあったようだが、良く知られているものはほとんど無い。また次に述べるSMP以前のAMPのマザーボードもわずかにある(SV-98 model3など)。

PCアーキテクチャで連続性のあるシステムのためには、対称型マルチプロセッシング (symmetric multi-processing, SMP) の必要があり、x86ではAPICを待たねばならなかった。APICには486以降が必要だった[19]。APICが内蔵されるのはP54C(Intel Pentium (1993年)#第二世代)コアからで、1990年代中頃のこととなる。[20]

なおP54C以降のコアだがTillamook(Mobile MMX Pentium)は非対応という情報がある[21]。

P54C以降のコアを採用したプロセッサにより、サーバ用途でのパーソナルコンピュータ類似製品では1990年代中頃から、デュアルソケットやクアッドソケットのマザーボードが現れるようになった(98ではPC-9821Rv20(および後継)がデュアルソケットである[22])。それが本格化するのはインテル チップセット(当時はインテル以外もチップセットを提供していたので、それらも含む)がマルチプロセッサに対応するようになってからである。そういったマザーボードにデュアルコアのPentium D(2005年)などを装着して、2x2=4 や 2x4=8 といった多数のマルチコア環境が現れている。

以上では、マルチコア化の前提となるマルチプロセッサ化がいかに可能となっていったか、を主に述べた。以下では、いかにしてマルチコア化が必須になっていったか、を述べる。

発熱と消費電力の問題

[編集]1990年代中頃からラップトップパソコンでの「腿(もも)が熱い」という発熱への不満やPCの放熱ファンの騒音が問題として認識され始めた。将来の汎用プロセッサは、製造プロセスの微細化によるリーク電流の増加や、処理能力向上を目的とした動作クロックの高速化によって、消費電力がますます増大していくことが予想された。当時の汎用プロセッサ処理速度の向上手法のままでは、汎用プロセッサのダイ温度が非現実的なまでに高温となり、冷却機構の物理的な限界から性能向上が頭打ちになることもまた予想された。2000年前後から一般ユーザー向けのPCでも水冷式の製品が販売されはじめた。

クロックの限界

[編集]2001年からは1GHzを越えるCPUクロックが一般的となり、2010年頃には5GHz前後まで伸びた。しかし、1GHzの1サイクルの時間内では、光速度でも30cmしか伝播できない物理法則の壁がある。そのため、今後さらにクロックが高速化されて5GHz以上や10GHzになれば従来のLCによる伝播遅延に加えて、電気信号そのものの伝播の遅さも無視できなくなってくる。

デナード則の崩壊

[編集]シングルコア性能の向上の限界

[編集]現在[いつ?]の汎用プロセッサ内部の処理機構がスーパースカラー機構などにより既に高度に高速処理への最適化がなされている。たとえば命令の先読みによって投機実行と呼ばれる、本当に実行が必要かまだ決まらない内から前もって次の処理を実行してしまうという動作を常に行う、汎用プロセッサの外部に主メモリがあるにもかかわらず汎用プロセッサ上にキャッシュメモリが3段階にも用意されている、さらにプリフェッチ・キューまでが用意されているといった具合である。他にもスーパーパイプライン、VLIW、アウト・オブ・オーダー実行等がある。これらの高速処理に欠かせない汎用プロセッサの回路は、それぞれがほんの少しだけ処理の高速化に貢献している回路であり、これ以上のさらなる付加回路を汎用プロセッサに追加してもそれほどの処理の高速化には貢献しないと予測される。

処理性能の向上策

[編集]マルチコア・プロセッサによってプロセッサ・コア数を増やした場合、OSやソフトウェアの対応により、システム全体の処理性能を向上させられることから、これら発熱とクロックの限界への解決策になる。

実際に今日の[いつ?]PCは動画や音楽データの再生やエンコードのように、マルチスレッドで性能向上を期待できる用途に使われることが増えている。

さらに、バックグラウンドで音楽を再生したりコンピュータウイルスのチェックを行なったりしながら、メールやWeb閲覧、文書作成、ゲームを楽しむことなどが行なわれており、複数のアプリケーションや多数のスレッドが実行される環境になっているため、マルチスレッドに対応するアプリケーションソフトウェアを利用していなくても、マルチコアの利点を享受することができる。

マルチコア・プロセッサの歴史

[編集]1999年、IBMは商用サーバ向けプロセッサでデュアルコアのPOWER4を発表し、CPUのマルチコア化をリードした。2004年5月にはインテルが従来のPentium 4の高速版でシングルコアCPUの開発コード「Tejas」の開発中止を決定したことが伝えられた。同じ頃、AMDも同社の計画から次世代のK9・K10などシリーズ以降の高速版CPUの開発を全て中止した。なお現在[いつ?]では、K8シリーズをマルチコア化の強化という新たな方向性で製品化したものをK10としている。

2005年になって、AMDは当初から消費電力を抑えマルチコア化を見越したK8アーキテクチャの設計を行い、デュアルコア製品の提供を開始した。製品名はDual-Core OpteronとAthlon 64 X2(のちにAthlon X2に改称)である。インテルは、マルチコアCPUの市場投入の出遅れをカバーするために、単純に2つのCPUのダイ (die) を1つのパッケージに封入したマルチコア・マルチダイ形式をとり、マルチコア・チップを早く出荷するというアプローチを取った。製品名ではPentium Dなど。近年[いつ?]では逆にAMDが設計の単純なマルチダイのOpteronチップを出荷する一方で、IntelはCPUコアのモジュール化によって派生ダイの製造を容易にし、リングバスの導入によりコア数の増減を容易にしているため、マルチダイの手段を取っていない。 また同じ2005年にはサン・マイクロシステムズはサーバ向けプロセッサUltraSPARC T1で8コアを実現した。

このほかPower Architecture系では、2006年リリースのCellが8コア[23]、2010年リリースのPOWER7が8コアである。

マルチコア・プロセッサの技術

[編集]ホモジニアスとヘテロジニアス

[編集]同種のコアを複数実装する「ホモジニアスマルチコア」と、異種のコアを実装する「ヘテロジニアスマルチコア」が存在する。

IBM、ソニー・コンピュータエンタテインメント、東芝の3社が共同開発しPlayStation 3に組み込まれているCellプロセッサは、1個の汎用的なプロセッサコアと、ストリーミング処理に特化した8個のシンプルなプロセッサコアを組み合わせた「ヘテロジニアスマルチコア」というアプローチをとっている。

Xbox 360のプロセッサ・コアは対称型マルチコアと呼ばれる3コアのプロセッサで、構造上はホモジニアスに属するものである。同時マルチスレッディング (SMT) をサポートし、最大6つのハードウェアスレッドを同時に駆動することができる。

米AMD社はさらなる高処理能力化への手法としてヘテロジニアスマルチコアプロセッサを計画し、Fusionプロジェクトと命名した。その手始めとして、グラフィックス処理装置 (Graphics Processing Unit, GPU) 開発企業であるカナダのATI社を2006年に買収し、GPUと汎用プロセッサを同一ダイに集積したCPU製品 (AMD Accelerated Processing Unit, APU) を登場させた。

また、命令セットの形式が同じコアを組み合わせたプロセッサのうち、ARMアーキテクチャのbig.LITTLEのように、処理能力(動作クロック周波数)の高いコアと処理能力の低いコアを組み合わせたプロセッサも、トランジスタ数や消費電力の点で有利な低コストのマルチコアと考えられる。同一命令セットという観点ではホモジニアスではあるが、処理能力の点では同一ではなくヘテロジニアスとなる。異種CPUトポロジー (heterogeneous CPU topologies) とも呼ばれる[24]。

電力管理

[編集]マルチコア化の目的の1つに低消費電力化がある。マルチコアに限らないが、多くの汎用プロセッサや専用プロセッサでは、使用しないコアのクロックを停止する「クロック・ゲーティング」、機能ブロックごとに電源供給を停止してリーク電流そのものを無くす「パワー・ゲーティング」が備わっている。

汎用プロセッサの中には他のコアを停止する代わりに1つのコアだけ供給電圧やクロックを高めてシングルコアでの処理性能を高める技術も導入が予定されている。機能ブロックごとにスレッシュホールド電圧値を変えて動作速度を変えるのは「マルチVth」と呼ばれる。マルチコアでは、機能ブロックごとでしか行なえなかったシングルコア製品よりさらに進んだ電力と処理性能との最適化機能が取り込まれる。

メモリ・ボトルネックの解消

[編集]現代のプロセッサはノイマン型であるため、ノイマンズ・ボトルネックによる処理速度の制約がある。2009年現在の主記憶装置に使われるDRAMの速度はプロセッサに比べて極めて遅く、この速度差を解消するメモリ技術は未だに現れていない。

シングルコアでは、プロセッサ内部に小容量のキャッシュメモリを何階層も重ねて持つなど、遅い主記憶装置でもプロセッサの処理性能を大きく損なうことを避けてきたが、複数のプロセッサ・コアを単一の主記憶装置へ接続することは、メモリアクセスによるボトルネックが顕在化する危険性をはらんでいる。

- 主記憶装置アクセスの高速化

- 代表的なプロセッサ・メーカー2社[どれ?]は、外部(ノースブリッジ)にあったDRAMコントローラーをマルチコア・プロセッサに取り込み、これらのアクセス信号線を高速化するなど主記憶装置への帯域幅を広げることで対応する予定である。

- キャッシュシステムの高度化

- 主記憶装置であるDRAMとプロセッサ側との速度差はマルチコアの採用によって一層拡大するため、シングルコア以上にキャッシュシステムによるメモリ帯域幅の確保は重要となる。

- 幸い、プリフェッチへの努力をある程度あきらめることで、そういった回路へ割いていたトランジスタが削減できてそれぞれのプロセッサ・コアを小さく作れるため、プロセスルールの微細化による恩恵も続くことに合わせて、複数のプロセッサ・コアを1つのダイに載せてもなお、充分な容量のローカルキャッシュを作り込む余裕が生まれる。

- 各コアごとにローカルでキャッシュを持つことはアクセス・スピードでは有利になるが、互いのローカル・キャッシュの内容を同一に保つスヌープ機構が複雑になり、各ローカル・キャッシュを共有し合う機構ではさらに複雑になる[25]。このため、複数のコアの配下で3レベルにもなるキャッシュ階層同士が最適の調停機構を実現するにはこれまでのプリフェッチへの努力とは違った種類の複雑で高速動作が求められる回路がダイの上で大きな面積を占めるようになる。この新たなキャッシュコントローラー部はかなり電力を消費するが、少しでも主記憶装置への無駄なアクセスが減らせるのであれば消費電力は総合的には削減できるとされる。

冗長構成

[編集]メモリ半導体ではあらかじめ冗長領域を設けて不良を少なくする工夫が行なわれているが、マルチコアの登場によって演算部であるコアも同様の冗長的な編成が可能となっている。ソニー・コンピュータエンタテインメントのCellプロセッサでは8個あるコア相当のSPEの内、実際に有効化するSPEは7個とした。こうすることで1個のSPEの動作不良な量産ダイの中でも出荷可能となり、歩留まりが向上する。米インテル社から将来出荷予定のNehalemでもキャッシュメモリの冗長化だけでなく不良コアを無効化する機能が付くと公表されている。

プロセッサ例

[編集]汎用プロセッサ

[編集]- IBMのPOWERシリーズ(POWER4以降)

- サン・マイクロシステムズのRock

- 富士通のSPARC64(VI以降)

- AMD (x86/x64) のAthlon X2、Phenom II、Opteron、AMD FX、Ryzen/EPYC(Zen)

- インテル (x86/x64) のCore 2 Duo/Quad/Extreme、Core iシリーズ、Xeon。

- NetBurstマイクロアーキテクチャはPC向けに関してはシングルコアだったが、サーバー向けに関してはデュアルコア製品もあった。

- Coreマイクロアーキテクチャ採用のCore 2シリーズにてPC向けでもマルチコアが導入されたが、Core 2 Soloのようにモバイル向けではシングルコア製品もあった。

- NehalemマイクロアーキテクチャやSandy Bridgeマイクロアーキテクチャはシングルコア製品もあった。Ivy Bridgeマイクロアーキテクチャ以降はデュアルコア以上となった。

- インテル (IA-64) のItanium 2(Itanium 9000 / Montecito以降)

- ICTのGodson-3

- Apple Mシリーズ

なお、インテルは10個以上のコアを集積したプロセッサをメニーコアと呼んでいる[1]。

モバイルSoC

[編集]- クアルコム (ARM) のSnapdragon(S3以降)

- NVIDIA Tegra

- Apple Aシリーズ

専用プロセッサ

[編集]- Graphics Processing Unit (GPU) - NVIDIA GeForceやAMD Radeonなどに代表される。単純な演算器(ストリームプロセッサ)を束ねて、複数のデータをまとめて並列処理することに特化しており、CPUとは比較にならない超マルチコア構成(数百〜数千)となっている。ウルトラハイエンド製品では1万個を超えるコアを搭載しているものもある。リアルタイム3Dグラフィックスの描画が主な用途だが、汎用処理 (GPGPU) の各種APIにも対応している。

- インテルのXeon Phi - かつてコードネームLarrabeeとして開発されていた製品の後継として登場したコプロセッサだが、ラインナップ製品はすべて生産終了している。コア数は最大72個[26]。

- シスコシステムズのQFPネットワーク・プロセッサ - 40個

- D. E. Shaw ResearchのAnton

- トプスシステムズのTOPSTREAM - 最初からマルチコア向けに開発された日本製プロセッサ。MPEG-4および無線LANのベースバンド処理チップの実績あり。

組み込み系プロセッサ

[編集]汎用プロセッサでマルチコアが一般化する以前から、組み込みシステムではマルチコアは一般的に使われている。iPodに搭載されているPortalPlayerのチップは、「ARM7」のコアを2つ搭載している。

脚注

[編集]- ^ a b インテル、メニーコア化への取り組みなど、研究活動に関する説明会を開催[リンク切れ], マイコミジャーナル, 2005年11月09日

- ^ doi:10.1145/1465482.1465493

- ^ FACOM230-60(1968年) : 富士通2024年9月4日閲覧

- ^ FACOM 230-60 - コンピュータ博物館2024年9月4日閲覧

- ^ 日立評論1974年1月号:電子計算機および計測2024年9月4日閲覧

- ^ HITAC 8800, 8700 - コンピュータ博物館2024年9月4日閲覧

- ^ TOSBAC-5600/10, 30, 50 - コンピュータ博物館2024年9月4日閲覧

- ^ 技術の系統化調査報告「コンピュータ開発史概要と資料保存状況について -第3世代と第3.5世代コンピュータおよびスーパーコンピュータについて-」2024年9月4日閲覧、p. 28から引用「TOSBAC-5600は1970年に発表された汎用大型コンピュータで、密結合マルチプロセシングを前提に設計され、」

- ^ ACOSシリーズ77 システム600, 700 - コンピュータ博物館2024年9月4日閲覧

- ^ SXシリーズ 進化の軌跡 | NEC2024年9月4日閲覧、SX-3の項目に、引用「国産初の共有メモリ・マルチプロセッサによる並列処理や、」とある

- ^ SX-3シリーズ - コンピュータ博物館2024年9月4日閲覧

- ^ VPP500(1992年) : 富士通2024年9月4日閲覧

- ^ FUJITSU VPP500, VX/VPP300/VPP700シリーズ - コンピュータ博物館2024年9月4日閲覧

- ^ 日立評論1993年5月号:スーパーコンピュータシステムの動向2024年9月4日閲覧

- ^ HITAC S-3000シリーズ - コンピュータ博物館2024年9月4日閲覧(Descriptionメタタグに、日立:4台のマルチプロセッサ構成で32GFLOPSのベクトル演算性能を有する並列ベクトル型スーパーコンピュータS-3800/3600を発表、とある)

- ^ コンピュータグラフィックスシステムLINKS-1 - コンピュータ博物館2024年9月5日閲覧

- ^ 並列画像生成システムLINKS - 2のアーキテクチャ( http://id.nii.ac.jp/1001/00015340/ )

- ^ つくる並列処理コンピュータ - 東京電機大学出版局2024年9月5日閲覧

- ^ 486SXでも可かどうかはよくわからない。

- ^ デュアルソケット・ザ・ワールド 8086 Multiprocessing Features2024年9月5日閲覧

- ^ 企画課:特別企画 第2回 PC-98シリーズと CPU:第 5世代 CPU編2024年9月5日閲覧

- ^ 企画課:特別企画 第2回 PC-98シリーズと CPU:第 6世代 CPU2024年9月5日閲覧、Pentium II ODPの解説の最後を参照。

- ^ 設計上は9コアが存在するが、うち1コアは歩留まり向上のための予備であり、出荷前に無効化されている。

- ^ Energy Aware Scheduling — The Linux Kernel documentation

- ^ ローカル・キャッシュを共有し合う機構とは、コアローカルなL2キャッシュとダイ共有のL3キャッシュの関係で、通常はスヌープしてローカルなL2キャッシュ間のコヒーレンシを確保する仕組みである。自分のコアのL2でmissして他のコアのL2にあれば、L3ではなく他のコアのL2をアクセスする仕組みを指す。コア数が増えるとダイ共有のL3では対応し切れなくなるためと推測される[独自研究?]。

- ^ 製品仕様 インテル® Xeon Phi™ プロセッサー