MOSダイオード

MOSダイオードは、MOS(Metal-Oxide-Semiconductor、金属-酸化物-半導体)構造をもつダイオード[1] である。MOSキャパシタとも呼ばれる。

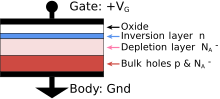

P型またはN型のシリコンウェハの表面を酸化して絶縁酸化膜(SiO2)を作り、その上に金属ゲート(金属や高濃度にドーピングされたシリコン)を付けた構造をもつ。

MOSキャパシタは、ランダムアクセスメモリ(RAM)やCCDイメージセンサに用いられる。

エネルギーバンド図

[編集]p型シリコンMOSキャパシタのエネルギーバンドを考える。熱平衡状態にあるMOSキャパシタでは、金属ゲートと半導体との仕事関数が異なるため、酸化物と半導体表面のバンドが曲がる。その結果フェルミ準位が価電子帯から離れるため空乏層が形成する。

p型MOSキャパシタに負のゲート電圧をかけると、シリコン基板のバンドが平らになる電圧が存在する。このときの電圧をフラットバンド電圧と呼ぶ。この状態ではシリコン基板中に電界が存在していない。さらに負の方向へ電圧をかけると、p型基板の自由可動電荷である正孔がゲート界面に引き付けられ、シリコンのバンドが上に曲がることによってフェルミ準位が価電子帯に近づき、半導体表面では正孔が溜まる。これを蓄積と呼ぶ。

逆にMOSキャパシタに正の方向へ電圧を加えると、バンドが下に曲がることでフェルミ準位は価電子帯からさらに遠ざかり、正孔が移動することで空乏が進む。またある電圧を超えると、フェルミ準位が伝導帯に近づくことで少数キャリアである電子が半導体表面に誘起される。これを反転と呼び、半導体表面の少数キャリアの層を反転層と呼ぶ。反転が始まる電圧をしきい値電圧と呼ぶ。

実際にはフラットバンド電圧を超えてゲート電極の電圧を上げていくと、p型シリコン側の可動電荷である電子が追いやられて界面近くのシリコンが空乏化し、その空乏層に残された不純物イオンが固定電荷としてゲート電極による電界を受け止めるが、この段階では、まだ十分な電子が界面に誘起されていない。反転層として十分な電子が現れるのは、空乏層の固定電荷であるアクセプタ原子の密度と同等の電子密度になった場合であり、そのためには界面での(n型方向の)フェルミ準位が基板の(p型方向の)フェルミ準位とほぼ等しくなる必要がある。[2]

すなわち、p型基板のフェルミ準位がバンド中央の真性フェルミレベルから測ってだとすると、界面が反転するにはバンドがだけ曲がる必要があると言う事になる。一旦反転層に電子が蓄積されるようになると、それ以上に高い電圧をゲート電極に印加しても反転層の電子密度が高くなるだけで、空乏層の伸びはほぼ無視できるので余分な電圧はゲート絶縁膜に吸収されると考えてよい。従って、閾値電圧はゲート絶縁膜にかかる電圧とシリコンのバンドの曲がり分の合計になる。[3]

現実的には、ゲート絶縁膜中に存在する電荷や界面準位(Qss)によってフラットバンド電圧も変化するので、MOSキャパシタの閾値電圧はその影響も受ける。

-

接続前

-

熱平衡(空乏)

-

フラットバンド

-

蓄積

-

反転

容量-電圧特性

[編集]

右図にp型シリコンMOSキャパシタの容量とゲート電圧の関係(C-V特性)を示す。

ゲート電圧が負の方向に大きい場合(図の左側)、p型シリコンから酸化膜に向かう電場が生じる。その電場によってp型シリコンの多数キャリアである正孔は酸化膜/p型シリコン界面に溜まった状態となる(蓄積)。ゲート電圧に比例して界面の正孔濃度が変化するため、容量は酸化膜の容量となる。

ゲート電圧が負の値から正の方向へ大きくなると、MOS構造内の電場がゼロとなるゲート電圧(フラットバンド電圧)が存在する。

ゲート電圧がフラットバンド電圧よりも正の方向へ大きくなると(図の中央)、酸化膜からp型シリコンへ向かう電場が生じる。その電場によって、正孔は酸化膜/p型シリコン界面から遠ざけられ、界面の正孔が不足する(空乏)。全体の容量は酸化膜の容量と空乏層の容量との直列になるため、容量は低下する。

さらにゲート電圧が正の方向に大きくなると(図の右側)、まずシリコンのバンドが酸化膜を通して押し下げられ、 それによってp型シリコン中の正孔が酸化膜界面から遠ざかり自由な可動電荷のない空乏層が形成される。 そのためMOSのゲート・シリコン間の容量は空乏層が広がるにつれてさらに小さくなっていく。(いわゆるdeep depletion、あるいは非平衡状態と言う)[4] 低温で光が遮断され、結晶欠陥も少ない基板であれば、deep depletion の状態は長く保たれ、分単位に及ぶこともある。

周囲にN型の拡散層が無ければ、時間と共に基板の少数キャリアである電子や、ボルツマン分布に従う電子・正孔の対生成、あるいは光による対生成によって生じた電子がゲート電極とシリコンの界面に集まる。(反転)。 反転層の生成後に低周波の交流電圧で測定した場合は、その交流電圧の変化に対応して反転層の電子の増減が生じるので、容量は酸化膜の容量となる。一方、測定を高周波の交流電圧で行った場合(青色)は電圧の変化に電子と正孔の生成が追い付かないため、反転層の電荷(この場合は電子)は増減せず、空乏層の微小な伸び縮みが反応するので測定値は、酸化膜の容量と空乏層の容量との直列容量のまま一定値となる。

ダイオード接続MOS

[編集]

エンハンスメントモードのNチャネルMOSFETのドレインとゲートを短絡した「ダイオード接続MOS」のことをMOSダイオードと呼ぶことがある。 ダイオード接続MOSは、ノーマリーオフ(エンハンスメントモード)のNチャネルMOSFETのドレインとゲートを短絡したもので、一般のダイオードに似た単方向性のある2極素子として扱うことができるが、原理上動作電位の制限などがある[5]。Vfが、PN接合ダイオードでは約0.6V・ショットキーバリアダイオードはもっと低いが、ダイオード接続MOSでは使用するFETの VGS(th) によって決まる。

MOS集積回路 (IC) 中ではこの他に、バルクと電極の間のいわゆる寄生ダイオードをPN接合ダイオードとして利用することもある。また、似たようなFETの使い方として、ノーマリーオン(depletionモード)のNチャネル接合型FET (JFET) のソースとゲートを短絡し、IDSSを利用するいわゆる定電流ダイオードがある。

参考文献

[編集]- S. M. ジー "半導体デバイス―基礎理論とプロセス技術"

- B. L. アンダーソン "半導体デバイスの基礎 (中)"

注

[編集]- ^ ダイオードと言ってもこの場合は整流作用がある訳ではなく、ゲート電極とシリコン基板電極と言う二つの電極を持つデバイスと言う意味である。

- ^ B.L.アンダーソン『半導体デバイスの基礎(中)』2012年、488頁

- ^ B.L.アンダーソン『半導体デバイスの基礎(中)』2012年、614頁

- ^ S. M. Szeの Physics of Semiconductor Devices によると、第一版では "nonequilibium condition" と表現されているが(p435)、第二版では "deep depletions" となっている(p372)。

- ^ 両極の動作電位が(正の)電源の前後であれば、Pチャネルを使うようにアレンジするなど。