MCP-1600

5個の40ピンパッケージに収まったMCP-1600 マイクロプロセッサ。WD16マイクロコードを搭載している。 | |

| 生産時期 | 1975年から |

|---|---|

| 生産者 | ウエスタンデジタル |

| CPU周波数 | 3.3 MHz から 3.3 MHz |

| 命令セット | 98 |

| パッケージ | 4個から5個の40-pin DIP (Dual in-line package) |

| 15 | 14 | 13 | 12 | 11 | 10 | 09 | 08 | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 | (bit position) |

| Register file |

LSI-11でのレジスタ名称[1] | |||||||||||||||

| R3 | R2 | PSW | ||||||||||||||

| R5 | R4 | Desination | ||||||||||||||

| R7 | R6 | Source | ||||||||||||||

| R9 | R8 | Bus address | ||||||||||||||

| RB | RA | Instruction register | ||||||||||||||

| RD/GD | RC/GC | R7 (PC) | ||||||||||||||

| RF/GF | RE/GE | R6 (SP) | ||||||||||||||

| GB | GA | R5 | ||||||||||||||

| G9 | G8 | R4 | ||||||||||||||

| G7 | G6 | R3 | ||||||||||||||

| G5 | G4 | R2 | ||||||||||||||

| G3 | G2 | R1 | ||||||||||||||

| G1 | G0 | R0 | ||||||||||||||

| Control registers | ||||||||||||||||

| G | Register Pointer | |||||||||||||||

| LC | Location Counter | |||||||||||||||

| RR | Return Register | |||||||||||||||

| TR1 | TR0 | Translation Register | ||||||||||||||

| Status register | ||||||||||||||||

| NB | ZB | C4 | C8 | N | Z | V | C | ALU status/Flags | ||||||||

MCP-1600は、1975年にウエスタンデジタルによって発売された複数チップ構成の16ビットマイクロプロセッサである。1980年代初頭まで製造された[2][3] 。 Pascal MicroEngine、Alpha MicrosystemsAM-100のWD16プロセッサ、そしてDEC LSI-11マイクロコンピューターで使用された[4]。 DEC PDP-11のコストを削減し、小型化した実装である。

解説

[編集]チップセットに3種類のチップが存在する。

- CP1611 RALU - レジスタ・ALUチップ

- CP1621 CON - 制御チップ

- CP1631 MICROM - プログラムされたマイクロコードが入ったマスクROMチップ(512ワード。1ワードは22ビット)

これらのチップは、3.3 MHzの4相クロックと3つの電源電圧 (+5V, +12V, -5V) を使用した。 当時、ウエスタンデジタルで利用可能だったNチャネルシリコンゲートプロセスによって製造された。 内部的にMCP-1600は、(比較的高速な)8ビットプロセッサである。その8ビットプロセッサは、16ビットCPUをエミュレートするためにマイクロコードでプログラムすることができた。 全てのバイト長命令は、1クロックで実行できる。ワード長命令と分岐命令は、2クロック必要だった。 4個までのMICROMがサポートされたが、1つのプロセッサに必要とされるのは、通常2個あるいは3個であった[5]。

レジスタファイルは、26個の8ビットレジスタで構成されている。 10個のレジスタ(RX)は、マイクロ命令によって直接アドレスされる。 4個のレジスタ(Rx/Gx)は、直接あるいは間接のどちらでもアドレスされる。 そして、残りの12個のレジスタ(Gx)は、間接的にしかアドレスされない。 間接アドレッシングは、3ビットのGレジスタを使って行われた。Gレジスタは、PDP-11命令のレジスタフィールドの値が常にロードされている[1]。

MCP-1600の最も重要な機能は、プログラマブル・トランスレーション・アレイ(PTA)である。 PTAは、数個のパラメーターを持つ機能に対応するマイクロ命令の読み出しアドレスを新しく生成するための機能である。 これらのパラメーターは、マクロ命令(エミュレートされるCPUの命令)のデコード時に通常考慮されるものである。 PTAは、マクロ命令の翻訳のオーバーヘッドのほとんどを削減するために特別に設計されたものであった。

本質的にマクロ命令のオペコードは、一つのアドレスに素早く翻訳される。そのアドレスは、Location Counter へロードされ、マクロ命令を処理するための適切なマイクロ命令への分岐アドレスを作る[5]。

ジョン・ウォレス(John Wallace)は、プロジェクトマネージャーであり、CP1621を設計した。 マイク・ブリナー(Mike Briner)は、CP1611を設計し、後にSilicon Storage Technologyでシニア・バイスプレジデントになった。 ビル・ポールマン(Bill Pohlman)は、設計エンジニアリングマネージャーであり、後にIntel 8086プロセッサのプロジェクトマネージャーになった。

1976年にナショナル セミコンダクターがMCP-1600のセカンドソース品を製造・販売するだろうという発表がされた。 実際にナショナルセミコンダクターが製造したものが存在するのかどうかは不明である[6]。

CP1611とCP1621のクローンが、KR581IK1とKR581IK2(ロシア語: КР581ИК1とКР581ИК2)という名称でソビエト連邦で製造されていた[7] ソビエトの581シリーズは、MCP-1600ファミリーの他のチップも含んでいた[8]。

シミュレーター

[編集]cp16simは、オープンソースのMCP-1600のシミュレーターである。 C言語で書かれており、MCP-1600プロセッサをエミュレートする。そのPLAは、WD900 Pascal Microengine プロセッサのマイクロ命令を実行する。 2016年現在、未完成である。 「雑草に入る(苦境に陥る)前に ACD PDQ-3 boot ROM の最初の数ダースのPコード命令を実行する程度には動作する。」という評判である。 GNU General Public Licenseバージョン3の下でリリースされている[9]。

ギャラリー

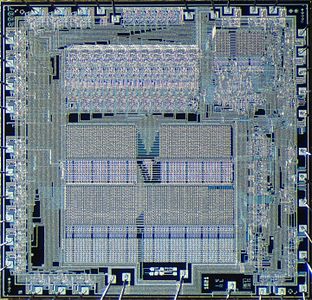

[編集]- LSI-11チップセットのダイの写真

-

CP1611 RALU

-

CP1621 Control

-

CP1631 MICROM

出典

[編集]- ^ a b Bell, C. Gordon (1978). Computer Engineering: A DEC View of Hardware Systems Design (4th Printing ed.). Digital Equipment Corporation. ISBN 1-483207-67-6 29 July 2022閲覧。

- ^ “Western Digital adds MCP-1600 Micro”. Computerworld. (26 November 1975).

- ^ “Western Digital 1600”. AntiqueTech. 3 January 2017時点のオリジナルよりアーカイブ。5 January 2017閲覧。

- ^ “Western & DEC have 3-Chip uC Mini”. Microcomputer Digest 1 (6): 7. (December 1974) 11 January 2023閲覧。.

- ^ a b MCP-1600 Microprocessor Users Manual. Western Digital. (1975) 28 April 2022閲覧。

- ^ “MCP 1600 Second Sourced”. Modern Data 9 (3): 40. (March 1976) 7 November 2022閲覧。.

- ^ “Soviet microprocessors, microcontrollers, FPU chips and their western analogs”. CPU-world. 2020年4月18日閲覧。

- ^ Козак, Виктор Романович (24 May 2014). “Номенклатура интегральных микросхем — Микропроцессоры: серии 580 - 589” [Nomenclature of integrated circuits — Microprocessors: Series 580 - 589] (Russian). 24 March 2016閲覧。

- ^ “Microcode-Level Simulator for Western Digital MCP1600”. Github. 25 December 2022閲覧。