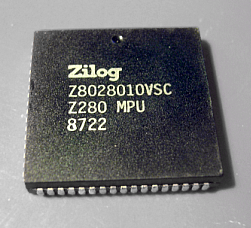

Z280

Z280 は、ザイログが1987年に発表した16ビットマイクロプロセッサであり、Z80とのバイナリー互換を保った形の製品で、しかも最大25MHzまで動作周波数を引き上げ可能だった。NMOS版Z800のZ8216バージョン(データバスはZ-BUSで16ビット幅、MMUは16MBサポートのバージョン)を若干改良した CMOS 版に基づいているが[1]、ブート時のコンフィギュレーションにより、外部バスを8ビット幅のZ80バスに設定することも出来る。ライバル各社からは1980年にはMotorolaがMC68000を発表、1982年にはIntelの80286も登場しており、その影響でZ280は商業的には完全な失敗となった。

概要

[編集]

メモリ管理ユニット (MMU) を内蔵し、アドレス空間を 16 MB に拡張し、マルチタスクとマルチプロセッサ機能を備え、コプロセッサ構成が可能で、256バイトのキャッシュメモリを備え、命令やアドレッシングモードも豊富であった(組合せは2000以上)。ハードウェア乗算、除算、符号拡張を含む32ビットデータ演算を効率的に処理することができる。スーパーバイザーとユーザーの動作モードがあり、オプションで両モードで命令とデータ用に別々のアドレス空間を使用できる(合計4つのアドレス空間が可能)。

内部のクロック信号は外部クロック信号の1倍、2倍、4倍の速度で動作するように設定でき(例えば、バスが4MHzなら、CPUは16MHz)、Z80とは異なり、Z280はアドレス・バスとデータ・バスに多重化配置を採用している。

特徴的な機能

[編集]Z280は、当時としては先進的な次のような機能を数多く備えていたが、そのほとんどは、Zilog製プロセッサーでは二度と見られないものだった[2]。

- オンチップ命令、and/or データキャッシュ、またはオンチップRAM

- 命令パイプライン化

- 高性能16ビットZ-BUSインターフェイス、または8ビットZ80互換バス・インターフェイス

- メモリ保護機能付きMMU内蔵[3]

- 命令JAFとJARでどのレジスタ・セットがコンテキストにあるかを決定する機能

- 3つのオンチップ16ビット カウンタ/タイマー

- 4つのオンチップDMAチャネル

- オンチップ全二重UART

- ユーザーI/Oトラップ

- スーパーバイザモード(特権命令)

- 不正命令トラップ

- コプロセッサ・エミュレーション・トラップ

- バーストモードメモリアクセス

- 多くのバス構成モードを備えたマルチプロセッサ・サポート

- アクセラレーション通信インターフェイスによる複数の外部コプロセッサのサポート

- 複数のI/Oページ。eZ80のようにI/Oポートのアドレス範囲を制限したり、Z180のように既存のマザーボードデバイスと競合したりすることなく、内部I/Oデバイスも使用可能。

- スタックオーバーフロー警告

商業的には不成功

[編集]Z80の拡張としては、1986年に日立製作所が発表したHD64180や2001年にザイログが発表したeZ80などの方が商業的には成功している。

この記事は2008年11月1日以前にFree On-line Dictionary of Computingから取得した項目の資料を元に、GFDL バージョン1.3以降の「RELICENSING」(再ライセンス) 条件に基づいて組み込まれている。

脚注・参考文献

[編集]- ^ EDN November 27, 1986 p133

- ^ Z280 MPU Microprocessor Unit Preliminary Technical Manual. San Jose, California: Zilog. (1989). オリジナルの2019-09-11時点におけるアーカイブ。 2009年7月15日閲覧。

- ^ “Zilog Z280 MPU”. www.st.rim.or.jp. 2024年5月16日閲覧。

- Z80 Family Data Book. San Jose, California: Zilog. (January 1989)

- Reh, Tilmann (1991-09-16). “The CPU280 and Z280”. TCJ 2009年7月15日閲覧。.

関連文献

[編集]- Harston, J.G. (1998年4月15日). “Full Z280 Opcode List”. 2023年12月14日閲覧。

関連項目

[編集]外部リンク

[編集]- “Z280 データブック”. Oracle. 2023年12月14日閲覧。