相変化メモリ

この記事は英語版の対応するページを翻訳することにより充実させることができます。(2024年5月) 翻訳前に重要な指示を読むには右にある[表示]をクリックしてください。

|

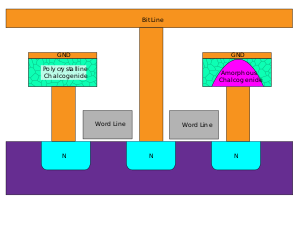

相変化メモリ(そうへんかメモリ、英: Phase-change memory)は、相変化記録技術を利用した不揮発性メモリである。PCRAM・PRAM・PCM・PCME・OUM (Ovonic unified memory)・C-RAMとも呼ばれる。

PCMは、カルコゲン化物ガラスの特異な性質を利用している。結晶相は低抵抗でアモルファス相は高抵抗である事を利用してデータの記録に利用する。書き込みは素子への熱変化により行う。

一世代前のPCMは、通常TiNから成る熱源に電流を流し、急激にカルコゲン化物ガラスを加熱・急冷することにより結晶相からアモルファス相に変化させ、再び一定時間結晶化温度に保つことで結晶相に戻すことができる。

PCMはまた抵抗値が様々な中間状態で変化するため、1セルに対して多値情報を記録することができる。しかしながら抵抗変化での多値記録は非常に難しく、フラッシュメモリーなどの他の多値技術においては用いられていない。

最新のPCM技術の本流は2つある。一つはGe2Sb2Te5(GST)に代わるような実用材料を発見しようとする研究グループであり、一定の成功を収めている。もう一つはGeTe/Sb2Te3 超格子構造を用い、レーザーパルスによってGe原子の配位状態を変化させることで熱を用いない相変化を実現しようとする研究グループである。この界面相変化メモリ(Interfacial Phase-Change Memory、IPCM)は多くの成功をおさめ、多くの精力的な研究が今でも続けられている[1]。

DRAMとの違いはキャパシター部分を相変化膜に置き換えただけであり、従来の製造プロセスと親和性が高く、技術的に共通点が多く、既存の設備を流用し易い。

背景

[編集]1960年代、エナジー・コンバージョン・デバイセズ社のスタンフォード・ロバート・オブシンスキーは初めてメモリとしての可能性を持つカルコゲン化物ガラスの性質について研究した。1969年には、C. H. Sieらはアイオワ州立大学にてカルコゲン化物ガラスとダイオードアレイを集積化することで相変化メモリとして利用できることを示す論文を出版した[2][3]。

1970年代に行われた研究によって、カルコゲン化物ガラスでのPCMの起源は電界誘起での細線結晶成長が関わっているということが明らかにされた[4][5]。1970年の9月、Intel社の共同設立者であるゴードン・ムーアは、PCMに関する記事をw:Electronics 誌に投稿したが、当時は品質や消費電力に問題があるとされPCM技術の実用化には至らなかった。

近年では、フラッシュメモリやDRAM技術が微細化の限界に達しつつある中で再び注目を浴び、研究されるようになっている[6]。

特徴

[編集]カルコゲン化物ガラスの結晶相とアモルファス相は大きく抵抗値が異なる。アモルファス相では非常に高抵抗で、結晶相では低抵抗であるため、これを0と1に対応させることができる。カルコゲン化物はCD-RWやDVD-RW等の書き換え可能な光学メディアと同じ材料である。これらの材料ではこれまで電気抵抗変化よりも、カルコゲン化物の反射率が変化するという光学的な特性が利用されてきた。

おおよそ全ての試作段階のPCMは、GSTと呼ばれるゲルマニウム(Ge)、アンチモン(Sb)、テルル(Te)のカルコゲン化物合金が利用されている。Ge:Sb:Teの組成比は2:2:5である。GSTは600 ℃以上に熱せられると、結晶性が失われる。一旦冷やされると、アモルファスのガラス的な状態に転移し、電気抵抗が高くなる。カルコゲン化物を結晶点以上(ただし融点より低い温度)に熱すると結晶状態に戻り、抵抗は低くなる。

この相変化が起きるまでの結晶化時間は温度に依存する。加熱が足りなかったカルコゲン化物部分は結晶化するのにより大きな時間を要し、そして過熱してしまった部分は溶けてしまうかもしれない。

通常、100 ns程度の結晶化時間が用いられることが多い[7]。これはスイッチング時間が2 ns程度であるDRAMのような通常の不揮発性メモリよりも長い時間である。しかしながら、2006年の一月にサムスン電子はPCMのスイッチング時間が5 nsにも達することを示唆している。

Intel社やSTM社による先進的な研究成果によって、カルコゲン化物の相状態をより細かく制御することができるようになり、1つのセルから4つの別々の状態に相変化できるようになった。つまり、前述のアモルファス相と結晶相(×2)、それぞれに部分的に結晶化した相があるかないか(×2)の計4状態である。それぞれの4つの状態は異なる電気的特性を持ち、電気的に読み出すことができるため、一つのセルに対して2bitを有するメモリとなる[8]。

PCMのセルを選択するには、ダイオードやバイポーラ接合トランジスタ(Bipolar Junction Transistor、BJT)やMOSFET等を用いることができる。ダイオードやBJTを用いることで、十分な電流を流すことができる。しかしながら、ダイオードは高電圧を必要とすることや隣のセル間での寄生電流が生じることから消費電力は高くなってしまう。

カルコゲン化物部分の抵抗はダイオードの抵抗よりも高い必要があるため、ダイオードからの十分な順バイアス電流を確保するには、必然的に動作電圧は1 V以上でなければならない。また、大容量のメモリセルをダイオードで選択する際に特に問題になるのは、選択していないセルの逆バイアスリーク電流である。一方、トランジスタによってセルを選択する際には、選択されたビットのみが逆バイアスリーク電流に寄与する。このリーク電流の大きさの違いは、数桁にも達する。

薄膜形状のセレクタは高密度化に有利であり、メモリ層を垂直方向に積層することによってセル面積を 4 F2以下にすることが可能である。オンオフ比が十分大きくない場合、アイソレーション特性はしばしばトランジスタを用いた場合には劣り、大容量での動作には不向きとなる。これまで、カルコゲン化物タイプの閾値スイッチが高密度なPCMセルアレイとして用いられることが示されている[9]。

フラッシュメモリと相変化メモリとの比較

[編集]書き込み時間

[編集]フラッシュメモリはMOSトランジスタのフローティングゲートに電子を出し入れすることによって情報を保持することができる。フローティングゲート内に電子を注入することで、トランジスタの閾値電圧をシフトすることができ、ビットとして記録することができる。例えば、閾値電圧が高い状態か低い状態かを、ビットの0と1に対応することができる。

ビットの状態を変える際には、フローティングゲートに溜まった電荷を一旦排出する必要があり、これは比較的高電圧をゲートに印加することによって行われる。この高電圧は出力までにやや時間のかかるチャージポンプ回路によって供給されている。したがって、通常のフラッシュメモリの(1ブロックの)書き込み時間はおおよそ100 µs程度であり、非常に遅い。例えば、SRAMの(1バイトの)読み込み時間10 nsと比較するとこれは10,000倍の遅さである。

一方、PCMは高速な書き込みが必要な場合にはフラッシュよりもずっと高い性能を示す。これは、メモリの要素がより早くスイッチングし、またフラッシュメモリと異なり1ビットを書き変える前に全てのブロックのデータを消す必要がないからである。PCMは通常のハードディスクの数千倍高速であるので、現在メモリアクセス時間によって性能が制限されている不揮発性メモリの役割を興味深いものに変えるかもしれない。

相変化メモリ(PCM)のスイッチング時間とそのスケーラビリティは非常に魅力的である[10]。最も顕著な欠点は、PCMが温度変化の影響を受けやすいことである。実際に大量生産ラインに組み込む際には、生産プロセスを改良する必要があるだろう。

寿命

[編集]フラッシュメモリは、書き込みのために高電圧を印加することで酸化膜の劣化を引き起こす。書き込み電圧はスケーリングに伴って小さくならないため、セルサイズが小さくなるにつれ書き込みの際のダメージは大きくなる。そのため、大抵のフラッシュデバイスは現在1セクタあたり5,000回程度の書き換えしかできず、多くのフラッシュデバイスはコントローラ側でウェアレベリング技術を用いて寿命を延ばしている。

PCMもまた使用のたびに劣化していくが、フラッシュとは異なる原因で劣化し、そしてフラッシュと比べて劣化のスピードは遅い。PCMは100万回の書き込みにも耐えうるとされている[11]。ただし、PCMの寿命は、書き込み時のGSTの熱膨張による劣化、金属やその他の元素の拡散、等によって制限されてしまう。

熱耐性

[編集]フラッシュメモリは、ボード上にはんだ付けする前にプログラムを書き込むことができるが、PCMははんだ付けをしてボードに取り付ける際の高温によってデータが消えてしまう。これは、近年の環境に配慮した鉛フリーはんだ(融解に高温が必要)を推奨していく動きとは相容れないものである。

したがって、PCMを用いるデバイスは、はんだ付けの後にデバイス自身が書き込みを行えるようなシステムを取らなければならない。

データ保持能力

[編集]フラッシュメモリで用いられるフローティングゲートは、時間とともにリークしてしまい、故障やデータ破損を引き起こす。フローティングゲートに注入する電子の数を精密に制御することで、フラッシュメモリは多値情報を1つのセルに記録することができる。実際、それによってメモリの密度を2倍にし、コストを下げている。

一方PCMでは、メモリの抵抗要素は比較的安定である。85℃の動作温度で、300年間データ保持が可能であるとされている[12]。PCMは基本的には1セルに1ビットしか記録できないが、近年Intel社はこの問題を解決しつつある。

フラッシュメモリはデータ記憶の際に電子をトラップしているため、放射線によってデータが破壊されやすく、それ故に航空宇宙機や軍事的な用途としては用いられない。その点、PCMは放射線に対して耐性がある。

技術的困難

[編集]PCMの問題点は、書き込み電流密度が大きいことである(>107 A/cm²[要出典])。相変化が起きる高温部分とそれに接する絶縁体との間のコンタクトもまた大きな問題である。この絶縁体は高い温度ではリークしてしまう可能性や、相変化物質とは異なる割合で膨張すると密着性が悪くなるという懸念がある。

PCMは書き込み時のレイテンシが大きいことと、高い消費電力によりこれまで実用は困難であったが、近年ではこの問題を解決するための多くの技術が提案されている[13][14]。

相変化メモリは、「書き込み時に急速に相変化させたい / 待機状態では相変化させたくない」というトレードオフが存在する。これは主に相変化が電気的でなく熱的に起こるものだからである。結晶化温度は常温と近すぎてはならない。近すぎると、データを長い間保持することはできないからである。結晶化に至るまでに適当な活性化エネルギーがあれば、書き込み時のみに急速に結晶化し、通常動作では殆ど結晶化が進まないような動作も可能である。

おそらく、PCMの最も大きな困難の一つは、長期での抵抗変化と閾値電圧のドリフトであろう[15]。アモルファス相の抵抗は時間に対してべき乗則(~ t0.1)に従ってゆっくりと増大していく。これは多値化動作に非常に大きな影響を与え、閾値電圧が設計値よりも増大した場合、基本的な2値動作でさえも動作が不安定になる。

2010年4月、ニューモニクス社は128 MB NORフラッシュを置き換えることを目的とした、Omneoと呼ばれるシリアル/パラレルインターフェースを持つPCMチップを発表した。彼らが置き換えを目論んでいるNORフラッシュは動作温度が-40~85 ℃ であったが、このPCMチップは0~70 ℃で動作するという点が異なる。つまり、PCMはNORフラッシュと比較して動作温度の制限が強いということを意味する。おそらく、書き込みの際に必要な大電流を供給するために、温度変化に敏感であるp-n接合を使用しているからである。

関連項目

[編集]外部リンク

[編集]- 読み書きが高速で耐久性に優れる「相変化メモリ」の低価格化へ向けた第一歩が実現 – GIGAZINE, 2016年5月18日

脚注

[編集]出典

[編集]- ^ Simpson, R.E.; P. Fons; A. V. Kolobov; T. Fukaya et al. (July 2011). “Interfacial phase-change memory”. Nature Nanotechnology 6: 501–505. Bibcode: 2011NatNa...6..501S. doi:10.1038/nnano.2011.96.

- ^ "Memory Devices Using Bistable Resistivity in Amorphous As-Te-Ge Films" C. H. Sie, PhD dissertation, Iowa State University, Proquest/UMI publication #69-20670, January 1969

- ^ Pohm, A; Sie, C; Uttecht, R; Kao, V; Agrawal, O (1970). “Chalcogenide glass bistable resistivity (Ovonic) memories”. IEEE Transactions on Magnetics (IEEE) 6 (3): 592. doi:10.1109/TMAG.1970.1066920.

- ^ "Electric-Field Induced Filament Formation in As-Te-Ge Semiconductor" C.H. Sie, R. Uttecht, H. Stevenson, J. D. Griener and K. Raghavan , Journal of Non-Crystalline Solids, 2, 358–370,1970

- ^ “A Cinematic Study of Mechanisms of Phase Change Memory”. YouTube (2012年6月21日). 2013年9月17日閲覧。

- ^ “Is NAND flash memory a dying technology?”. Techworld. 2010年2月4日閲覧。

- ^ H. Horii et al.,2003 Symposium on VLSI Technology, 177–178 (2003).

- ^ A Memory Breakthrough, Kate Greene, Technology Review, 04-Feb-2008

- ^ I.V. Karpov, D. Kencke, D. Kau, S. Tang and G. Spadini, MRS Proceedings, Volume 1250, 2010

- ^ Simpson, R. E. (2010). “Toward the Ultimate Limit of Phase Change in Ge2Sb2Te5”. Nano Letters 10: 414–419. Bibcode: 2010NanoL..10..414S. doi:10.1021/nl902777z.

- ^ “Intel to Sample Phase Change Memory This Year”. 2007年3月23日時点のオリジナルよりアーカイブ。2007年6月30日閲覧。

- ^ Pirovano, Agostino; Redaelli,;rea; Pellizzer, Fabio; Ottogalli, Federica; Tosi, Marina; Ielmini, Daniele; Lacaita,;rea L; Bez, Roberto (2004). “Reliability study of phase-change nonvolatile memories”. IEEE Transactions on Device and Materials Reliability (IEEE) 4 (3): 422-427. doi:10.1109/TDMR.2004.836724. ISSN 1530-4388.

- ^ "A Survey of Power Management Techniques for Phase Change Memory", S. Mittal, IJCAET, 2015.

- ^ "A Survey Of Architectural Approaches for Managing Embedded DRAM and Non-volatile On-chip Caches", Mittal et al., TPDS, 2015.

- ^ Karpov, IV; Mitra, M; Kau, D; Spadini, G; Kryukov, YA; Karpov, VG (2007). “Fundamental drift of parameters in chalcogenide phase change memory”. Journal of Applied Physics (AIP Publishing) 102 (12). doi:10.1063/1.2825650.