パッケージ (電子部品)

電子部品のパッケージ(外周器:がいしゅうき)とは、電気製品を構成する個別部品の外形を構成する部分であり、通常は小さな電子部品を包む合成樹脂や金属、セラミックを指す。

機能・要求

[編集]電子部品を収めるパッケージの機能と要求には次のものがある。

- 中の素子を外部からの衝撃、湿度、熱、ガス、光線などから守ること

- 接続端子を保持して外部との間で正しく信号や電源を伝えること

- 製品の組み立てに適する形状をなすこと

- 内部で発生した熱を速やかに放熱すること[注 1]

- コストが安いこと

- 電子部品の機能を検査しやすいこと

- 製造社名、製品型番や製造番号、ピン番号といった表示を保持すること

- 可能な限り正規製品であり、類似製品との区別を示すこと

- 環境問題に対応すること[注 2]

また、デジタル半導体に代表される高性能電子部品の多くが動作周波数が高く消費電流も大きくなるため、寄生容量や電流抵抗の小さな短く太い接続端子と放熱性の良いパッケージが求められる[注 3]。携帯機器に使用される部品では小型化が求められる。

個別受動部品

[編集]

抵抗(レジスタ、抵抗器)やコンデンサ(キャパシタ)、コイル、小型トランス等が個別受動部品(ディスクリート・パーツ またはコンポーネント、discrete component)と呼ばれる。半導体部品である単品のダイオードもパッケージ形態として見れば、抵抗等と同じアキシャル部品の形態が多い。

1990年代からはプリント基板上に表面実装されるチップ部品の使用が増え始め、2009年現在ではアキシャル部品やラジアル部品の形態はかなり減りつつある。アキシャル(axial)と、ラジアル(radial)は、リード(導く、lead)線が取り付けられている方向の違いを表している。 個別受動部品の場合、表面実装用部品では専用の形状にされることが多いが、中にはリード型部品のリードを短くしただけのものもある[注 4]。

半導体部品

[編集]歴史

[編集]電気的接続については、銅板をエッチングしたリードフレームとともにチップを封止した端子形(挿入形)が一般的であったが、1980年代後半以降、リードをプリント基板の穴に通さず基板表面に片面からはんだ付けする表面実装方式のパッケージが導入され、現在に至るまで広く普及している。 また時代が進むにつれ端子の数も集積度の上昇や素子の多機能化により大きく増加したため、DIPやSIP、SOPといった従来のパッケージでは対応できない製品が増え、端子を微小化したQFPやLCC、底面に丸ピンを格子状に並べた剣山のようなPGA(Pin=ピンを Grid=格子状に Array=配置)などが導入された。 さらに大規模なLSIでは外部との接続が数千にも及ぶため、BGAなどの端子密度の高いパッケージを必要とする。交換する可能性がある部品はソケットによって実装することもある。

過去には、ICパッケージ上に他のICパッケージを載せる「ピギーバック」のものがあり、不揮発性メモリ内蔵のCPUなどで、ソフト開発時にメモリの交換を容易にする目的で使用された。1980年代に普及した、紫外線照射によって記憶内容を消去するUV-EPROMというメモリ半導体のパッケージには、石英ガラスの窓が付いていた。また、ICカードなどの内部情報を読み取られない「耐タンパー性」を要する用途向けの半導体部品では、1つの半導体チップ上にCPU、ROM、RAMなどの必要な論理回路の全てを含むことで、2-8本程度の外部接続端子だけ持つようにしているものがある。また近年ではPoPやPiPといった、ピギーパックの再来とも言える実装方法が普及し始めている。

材質

[編集]半導体のパッケージは、半導体と外部を電気的に接続する端子と、半導体を搭載・密封保持する封止材に分かれる。 かねてより、より高い信頼性をより長時間維持し、より取り扱いやすく、より低価格に製造できるような材料の開発のために努力が続けられてきたが、2000年代以降は、有害物質を含まない封止材の使用や、鉛などの有害物質を含まないはんだで信頼性の高い接続が可能であることが求められるようになり、残存有害物質だけでなく製造工程においても有害物質が発生しない封止材料や、鉛フリーはんだに適した特殊な表面加工をされた端子が用いられるようになってきた。

端子

[編集]外部と電気的な接続を行う端子やリードフレームには、鉄・ニッケル合金が使われることが多く[注 5]、銅が用いられることもある。BGAパッケージでは半球状のはんだが使われる。ソケットによる実装を想定した製品や高周波を扱う製品、高い信頼性が求められる製品では、端子に金メッキを施して酸化防止、浮遊容量の低減を図ることが多い。それ以外の製品では主にニッケル合金やはんだでめっきをしており、これには酸化防止や導通不良の低減に加えはんだのぬれ性を良くする効果がある。特殊な場合を除いて、酸化しやすい鉄や銅を露出したままとすることはない。

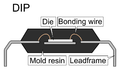

ダイを載せるリードフレームは端子と同時にプレス加工で作られることが多い。ダイのリードフレームへの固定では樹脂の他に、ダイとリードフレームの導通が必要な場合には銀粒子が含まれる樹脂ペーストや、放熱のために熱抵抗を下げる必要があればはんだも用いられる。端子とダイを接続するボンディングワイヤには金線やアルミ線が使われる[1]。

封止材

[編集]封止材の材質は、かつては金属(鉄、アルミ、真鍮など)がよく用いられたが、コストダウンや多ピン化への対応、小型化などの要求が出てくると、通常の温度・湿度の範囲で使うものはエポキシ樹脂など低価格な耐熱樹脂によるレジン・モールドが、また温度特性を広く必要とする工業用・軍事用や発熱が大きいデバイスではアルミナなどのセラミックが用いられるようになった。

金属やセラミックはあらかじめプレス及び焼結により成型しておき、内部にダイを実装した後に組み立てて、低融点ガラスなどシーリング材で密封する。一方、レジンモールドの場合は金型に入れて樹脂を射出成形する。テープ状パッケージでは、耐熱性と柔軟性の高いポリイミドで作られたテープ上にダイを実装する。近年ではプラスチックの性能が上がり、またプラスチック以外のパッケージでは表面実装部品のリフローはんだ付けが出来ないことなどもあり、セラミックを使用したパッケージは減少傾向にある。またダイオードでは当初よりガラス封止が多く使われ、現在では用途によりレジンモールドなどと使い分けられる。

レジンモールドはわずかながら水分を吸う。リフローはんだ付けをする場合、水分を含んだレジンモールドは急激な加熱によって破壊されることがある。これを防ぐため、メーカーから納入された部品は一定の個数ごとに袋などで密封して湿気から遮断されているが、開封した部品を全て直ちにはんだ付けするとは限らず、開封したまま長時間未使用になる部品が出ることは避けられない。そのような部品がそのままはんだ付けできるかどうか判断出来るよう、表面実装用の部品には開封後そのままリフローはんだ付けができる時間が決められており、データシートに記載されている。それを過ぎた部品は、水分を取り除くため決められた温度で予熱処理(ベーク)をしてからはんだ付けする。

CPUやチップセットといった非常に多くの端子を必要とする物では、パッケージ内部の接続にボンディング・ワイヤを使用しない「フリップチップ」接続を使用したパッケージが使われるようになった。これによりパッケージが薄く作ることができる上、プラスチック製であっても必要ならヒートスプレッダが使用でき熱抵抗が低くなったため、近年ではそれほどピン数が多くないが発熱が大きい製品にも使われ始め、旧来の金属製・セラミック製の製品を急速に置き換えている。スペースファクタを最大限に上げるため、大容量DRAM等ではダイに直接半田ボールをつけてレジンモールドした製品もある。

またフリップチップの登場に合わせ、従来のようにダイを丸ごと覆うのではなく、上に搭載するだけの「インターポーザ」が開発された。インターポーザはプリント基板の一種であり、したがって材料はプリント基板と同じガラス繊維入りエポキシが使われる。インターポーザとダイの隙間にはアンダーフィルと呼ばれる硬化剤を注入して固定する。インターポーザに実装したダイは上からさらにレジンモールドする場合もあるが、発熱の多い部品ではダイの上部を露出したままとしたり、ヒートスプレッダを装着することが多い。

規格

[編集]半導体パッケージの規格にはJEDECやJEITAなどがあるが、これらの規格で分類されないメーカー独自のパッケージも数多く存在する。また、メーカーのカタログやデータシートでは、必ずしもJEDECやJEITAの規格名称が使われるわけではなく、メーカー間の表記方法も統一されていない。

以下に半導体部品のパッケージについて記述する。

挿入形 (Pin insertion type)

[編集]箱型・缶状のパッケージから、プリント基板やソケットに差し込むリード線を出した形態を基本とする。初期の集積回路を代表する形態であり、近年においてもピン数が少ないトランジスタ、IC等で使われている。

-

DO-35パッケージのダイオード1N60

-

上からTO-3,TO-126,TO-92,SOT-23

-

TO-5型メタルCANパッケージの例

-

半導体レーザーダイオード

DOパッケージ (Diode Outline)

[編集]ダイオードに用いられるパッケージで、抵抗器などのアキシャルリードのものとほとんど同じである。 パッケージ材質はガラスやプラスチックのものが多いが、大電力用のダイオードでは金属缶パッケージに入れられているものもある。ただし、発光ダイオード、ダイオードブリッジなど特殊なダイオードのパッケージには使われない。

TOパッケージ (Transistor Outline)

[編集]Transistor Outlineの名の通り、トランジスタのパッケージとして開発されたが、各種IC、センサー、受動部品に至るまで幅広いデバイスに使用されている。パッケージ材質としては金属、セラミック、プラスチックがある。

- 金属

- メタルCANと呼ばれる缶状の金属に入れたもの。リードフレームの付いた金属の台座に素子を載せてボンディングし金属缶をかぶせたものと、金属缶の中にリードフレームを付けた素子を入れて底から樹脂を充填したものがある。ほとんどの場合、外装の金属部分は端子の1つとして内部素子に接続されている[注 6]。かつては多くの製品で使われたが、現在では一部での使用に限られ、オペアンプやセンサーなどではノイズや帯電を抑えること、パワートランジスタなどでは放熱を目的としている。現在では主に以下のデバイスで使用される。

- レーザーダイオード

- レーザーダイオードで波長を安定させるためには、温度一定に保持する必要があるため金属外装が使用される。また静電気及び電磁波を遮蔽する目的もある。

- センサー

- フォトダイオード等のセンサーで機器の外部にセンサーを露出させる場合、静電気による帯電を防止するために使用される。またGa系の半導体センサーを冷却して使用する必要がある場合にも金属の外装が使用される。

- 微小電力の増幅器

- 数ナノA以下の電流を扱う増幅器の場合、プリント回路板との浮遊容量を遮蔽するために使用される。

- トランジスタをパラレルまたはコンプリメンタリ・ペアで使用する

- TO-3など大型金属パッケージは他のパッケージより熱抵抗が小さいため、出力段に複数のトランジスタを使用する場合に個別のトランジスタの温度を揃え易い。主にマニア向けのアナログパワーアンプ等に使用される。

- セラミック

- 形状は短円柱状のものが多い。主に高周波用トランジスタに用いられたが、次第にプラスチック製パッケージにとって代わられた。

- プラスチック

- 形状は様々。小電力の製品は半円筒状のものが多い。ほとんどのTOパッケージはプラスチックである。箱状のピン数が多い物は後述のSIPと同じ。5ピン以上の製品はTO、SIPどちらとも呼べる。発熱の大きい電力用素子では背面にネジ穴の空いた金属板が露出するようになっており、ここに放熱器を取り付ける[注 7]。また表面実装型のTOパッケージは全てプラスチック製で、放熱板付きのものは基板上に広く半田付けして放熱するようになっている。

Intelの型番では最初のPrefixで"C"がCeramic-DIP、"D"がCer-DIP、"P"がPlastic-DIPであった。

DIP (Dual In-line Package)

[編集]「ディップ」と読み[注 8]、プラスチック製、またはセラミック製の本体から両側面から多数の金属製の接続端子が出て下方へ伸びた外形をしている[注 9][注 10]。

- Ceramic-DIP(セラミック・ディップ)

- リードフレームをあらかじめ挟み込んだセラミック製の容器にICチップを上部から入れてボンディングし、不活性ガス中で金属製の蓋をしたもの。リードフレームとピンは別々の部品であり、側面に露出したパッドにピンが1本ずつ金系はんだで取り付けられることからサイドブレイズドDIP[注 11]とも呼ばれる。信頼性及び対候、耐震性が高いため、医療、航空機、軍事用に使用されている。

- Cer-DIP(サー・ディップ、C-DIP)

- ボンディングされたICチップとリードフレームを2枚のセラミック板で挟み、低融点ガラス(ハーメチック)で封止するもの。ハーメチック・ディップと表現するメーカーもある[注 12]。セラミックDIP同様の長所を持ち、軍用・産業用に広く用いられている。

- Plastic-DIP(プラスチック・ディップ、P-DIP)

- ボンディングを済ませたICチップとリードフレームを金型に入れて樹脂を充填したもの。最も一般的なDIPパッケージである。産業用・民生用など幅広い用途に使われ、プラスチック材料の高性能化により過酷な状況での耐久性が向上してきたことからセラミック製のパッケージを置き換え始めている。

Ceramic-DIPとCer-DIPは共にセラミック製であり、熱抵抗がプラスチックより低いので放熱性が求められる製品で使用されることが多かったが、21世紀現在ではこれらは比較的少なくなっている。[注 13][2]

プラスチックのものはP-DIP(ピーディップ)とも表記されることがあり、汎用ロジックICなど多様なICに使われている。[注 14][注 15][注 16]

足を出す位置と間隔は、米テキサスインスツルメンツ社が米軍に製品を納入する際に定められたMIL規格に沿っていた。MIL規格が多くの点でデジタルICでの共通の規格となり、後にISO/IEC規格となった。後に登場するデジタルICのパッケージのサイズの多くはMIL規格を基準にしている[注 17]

-

セラミック・ディップ

拡大断面図 -

サー・ディップ

拡大断面図 -

プラスチック・ディップ

拡大断面図

SIP (Single In-line Package)

[編集]

パッケージの片側一列に足を出したもの。幅は狭くなるが、長さと高さが増える。ピン数をあまり増やせないため、小規模なICのパッケージに使われることが多い。ICだけでなく集合抵抗にもこのパッケージがよく使われる。 DIP形状と比べ放熱器を取り付けるのに都合が良いため、パワーアンプICやモータードライバICなど、ある程度発熱する部品に使われることも多い。

ZIP (Zigzag In-line Package)

[編集]SIPの足を左右交互に曲げてピン間隔を広げたもの。SIPに比べて横幅が小さくなり、ピン数を増やすことが出来る。ただし構造上、リード間隔が100ミルにならないことが多い。 SIPと同様、発熱の多い部品に使われることが多い。

PGA (Pin Grid Array)

[編集]

剣山のように格子状にピンを立てたもの、特にセラミック製をCPGA(Ceramic PGA)、ソケット実装専用のプラスチック製をPPGA(Plastic PGA)と呼ぶ。エポキシモールドではなくフリップチップ接続によりインターポーザ上にダイを載せたFC-PGA(Flip Chip PGA)も通常はPPGAに含める。ソケットにより容易に交換できることから、パーソナルコンピュータのCPUのパッケージとして多く採用されている。[注 18]

表面実装形

[編集]多層プリント基板技術の進歩と共に発展したのが表面実装型(Surface mount type)である。ダイをサブストレートに載せてワイヤ・ボンディングしたCSP (Chip size package) から、高密度に非常に多くの端子を接続するmBGA (Micro ball grid array) まで、プリント基板の多様性に伴い様々なパッケージ形態がある。現代の電子回路基板の多くは表面実装型ICを搭載している。表面実装技術 (SMT, Surface mount technology) によって回路基板上に高密度実装できるので製品の小型化とコスト低減が同時に実現出来る[注 19]。以下に表面実装形パッケージを示す。

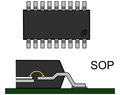

SOP (Small Outline Package)

[編集]対向する2辺から端子をガルウイング状に伸ばしたもので、小型のプラスチック・モールドのパッケージ。QFPの2辺にのみ端子を持つ形状ともいえる。SOIC (Small Outline Integrated Circuit) やDSO、SOと呼ぶこともある。SOPの薄いパッケージ形状のものを特にTSOP (Thin SOP) と呼び、さらにTSOPの横幅を狭めたものをTSSOP (Thin Shrink SOP)と呼ぶ。また、放熱用に底面に金属パッドを露出させたものもある。

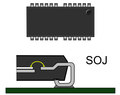

SOJ (Small Outline J-leaded)

[編集]リードをSOPとは逆に内側にJ型に曲げたもの。DRAMの単体ICパッケージでは、記憶容量の増大に応じたダイ・サイズの拡大をそれまでと同一のSOJパッケージに収めるため、大きくなったダイの上をポリイミド・フィルムで覆い、その上にリード・フレームを伸ばすLOC(Lead On Chip)という手法が採られるものがある[注 20]。ワイヤー・ボンディングはリード・フレームの隙間からダイに行い、リード・フレームへ接続する[2]。SOJはSOPと異なりソケットによる実装が可能で、後で交換する可能性のある部品に使われることも多い。

CFP (Ceramic Flat Package)

[編集]セラミック製の薄型パッケージで、構造的にはCeramic-DIPやCer-DIPを薄くしただけのものである。表面実装があまり普及していない時代に開発されたためピンが長く、曲げれば挿入型としても使用できる。軍用や高周波用デバイス向けとして開発されたが、薄く小さなセラミック板で素子を挟むという難しい製造方法のためCer-DIP以上にコスト高となった上、軍用用途では近年まであまり小型化の必要がなかったため、一部の高周波用デバイスや、スペースに厳しい制約があり、かつ過酷な環境で使われる用途のデバイスに使われたにとどまる。プラスチックの性能が著しく向上した現在では、プラスチック製のパッケージにほぼ完全に代替されている。

SOT (Small Outline Transistor)

[編集]その名の通りトランジスタのために開発された超小型パッケージで、TOパッケージと同様に様々な形状があるが、トランジスタ用のパッケージであるためピン数が3ピンのものからあることが大きな特徴である。 トランジスタだけでなくIC用にも広く使われている。同じ形状でもメーカーによって呼称にかなりばらつきがある。SOTとして規定されている形状は、一部TOパッケージの表面実装用のものと重複している。

QFP (Quad Flat Package)

[編集]QFP(Quad Flat Package) は、矩形本体の各辺から4方向に金属製の接続端子を延ばしたもの。SOPと同様に端子が細く長いものが多く、人が不用意に手で扱うと簡単に曲がる[注 21]。このため、4つの角にバンプの付いたものがある。 QFPよりさらに低背型のものに LQFP(Low Profile Quad Flat Package) と呼ばれるものや、さらに薄い TQFP(Thin Quad Flat Package) があり、放熱用にヒートスプレッダを内蔵したHQFP(Quad Flat Package with Heatspreader) がある[注 22]。

PLCC (Plastic leaded chip carrier)

[編集]PLCC(Plastic leaded chip carrier) はQFPの四方の端子をJ型に曲げたPlastic製のものである。QFJ(Quad Flat J-leaded Package)とも呼ばれる。LCCと名称が似ているが全く別のものである。Plasticでないものや素材を限定しないものはLCC(Leaded Chip Carrier)と呼ばれることがある。QFPより実装面積が小さくでき、ソケットによる実装も比較的多い。

-

SOP 上面図と拡大断面図

-

SOJ 上面図と拡大断面図

-

QFP 拡大断面図 図示されていないが、四方に端子が伸びる

-

PLCC 拡大断面図 四方に端子が出る

BGA (Ball grid array)

[編集]パッケージ底面の格子状に並んだ端子へディスペンサで溶けた半田を塗布し、半田の表面張力で半球状に形成された電極(バンプともいう)を持つ。表面実装で、リフロー炉ではんだ付けをする時に使われる。手作業による半田付けは不可能である。 QFPと比較して多数の電極を設けることが出来る上、周囲にリードが張り出さないので実装面積を縮小できる。ただし、外部からはんだ付けの状態を検査するのが困難となる。 また、一度はんだ付けしてしまうと部分的な修正や交換は専用の設備を持つ工場でもかなり困難である。取り外す時に基板を再加熱する必要があるため、多層構造の基板や後工程ですでに実装されている部品の耐熱規格によっては修理できない場合もある。外されたBGAに再びバンプを付けるのも、専用工具が必要な上に難易度が高い。 パッケージの熱膨張率と基板の熱膨張率が異なることから、通電中に発熱する素子の場合、電源投入と電源断を反復することによって熱膨張と収縮が繰り返され基板またはパッケージが歪み、はんだ付けされた接点にクラック(ひび割れ)を生じて断線状態となる故障が発生する可能性が高い。 ソケットによる実装は通常しないが、開発用途としてのソケットは存在するほか、ノートパソコンのCPUでの使用もまれにある。

TBGA(Tape Ball Grid Array)と呼ばれる、TAB技術によるフレキシブル基板をサブストレートに使用したBGAも存在する[3]。

MR-BGA(Metal Coating Rubber Ball grid array) 微小ゴム球体の表面に導電金属膜が形成された非溶融実装方式である。 接続したい電極パッドにふれるだけで実装並みの低抵抗値で通電が得られる。

ゴムが持つ弾力により反発圧力が発生して接触圧力が得られる仕組みで、 ゴム球体が低い荷重で押されると球面がフラットに変形して広い面積で電極パッドと接触し、低い抵抗値が得られる。

溶融を必要としないため完全常温状態での実装が可能で、また、ソケットのように取り外すことも可能で、実装サイズのコネクター接続を可能にしている。

アイデアとして1990年代から提唱されていたが、ゴムは熱膨張が極めて大きく、表面の導電金属膜を破壊することから実現が不可能とされてきたが、サッカーボールのようにゴム球体表面に熱膨張を抑えられる だけの厚さポリイミド外層を形成してゴムの熱膨張を抑制し、その上に導電金属層を形成することで破損しない構造となっている。

熱に弱いセンサーの実装、良好な高周波特性から金スタッドバンプの代替、取外し可能な構造、マイクロコネクターの小型高性能化への応用が期待されている。

LGA (Land grid array)

[編集]

BGAのはんだボールの代わりに平面電極パッドを格子状に並べたもの。 BGAと同様にリフローはんだ付けで使われる。 またBGAと異なりソケットによる実装が可能で、剣山型の電極に押し付けるようにして装着する専用ソケットを用いる場合もある。 米インテル社の多様なCPU用のLGA775、LGA115x系(LGA1156、LGA1155、LGA1150、LGA1151)、LGA1200、LGA1700、LGA1366、LGA2011、や、AMDのOpteron用のSocket F、Ryzen Threadripper用のSocket TR4、IBMのPOWERプロセッサ、NECのSX-8といった交換が想定されている多くのマイクロプロセッサに採用されている。

挿抜圧が生じないので多ピン接続に向き、面接触であるので異物が介在しない限り高い電力密度が保たれ、構造が単純なので物理的強度が高いなどが最先端CPUに採用されている理由であるが、接触抵抗を低く抑えて微小な異物程度の影響を避けるために、厚い金メッキ層が必要になりコスト高となる。

LLCC (Lead less chip carrier)

[編集]

セラミック表面に電極パッドを設け、リード線を出さないパッケージ。インテルの80286などで使われた。QFN (Quad flat no lead package) とも呼ばれる[注 23]。

TCP (Tape carrier package)

[編集]テープ・キャリア・パッケージは、ダイをキャリアテープと呼ばれるテープ状の樹脂フィルムに取り付けたものである。チップはキャリアテープ中央のデバイス・ホールに位置して、周囲からは接続線である細いインナーリードによって保持される。インナーリードは周囲に広がるに従って太くなり接続性の良い太いアウトリードとなってキャリアテープに張り付き固定されている。インナーリードとアウトリードはQFP同様に四方に出るのが一般的である。キャリアテープは写真フィルムのようにスプロケット・ホールが開いていて扱い易くなっている。[注 24]この実装方法をTAB(Tape Automated Bonding)と呼ぶ[3]。

LLP (Leadless Leadframe Package)

[編集]比較的小規模なICに用いられる超小型・薄型のパッケージ。MSOP、TSSOP、TQFPなどより小さいCSP用パッケージとしてナショナル セミコンダクターにより近年[いつ?]開発されたもので、LLPという名称は同社の登録商標である。プラスチック製の板状のパッケージの側面から底面にかけて電極パッドを露出させたもので、SOJやQFJの小型版ともLGAの小型版とも言える。厚みは0.8mm以下で、4辺に端子のあるものと2辺に端子のあるものがあり、底面に放熱パッドを備える。端子がパッケージの外に少しはみ出すタイプのものと、端子がパッケージの下に完全に隠れるタイプの2種がある。集合抵抗など受動部品のパッケージにも使用され始めている。

DFN (Dual Flatpack No-leaded)

[編集]LLPと良く似た構造の薄型・板状パッケージで、LLPと同様の特徴を持つCSP用パッケージ。パッケージの2辺または4辺にパッドを備え、底面に放熱パッドを持つ。1辺にのみパッドのあるものもある。4辺に端子のあるものはQFNとも呼ばれるが、これはLLCCの別名でもあり混同を避けるために全てDFNと呼ぶことも多い。 LLPとの構造上大きな相違点は、LLPの端子パッドがあらかじめ整形されてモールドの中に埋め込まれているのに対し、DFN/QFNではSOJのように側面から引き出した板状の端子を内側に折り曲げてパッドとしている点である[注 25]。 LLPが基本的にナショナルセミコンダクター社の製品のみで使われるのと異なり、DFNは多くの半導体メーカーで広く使われている。厚みは0.75mmが標準だが、より薄型化されたものもある。DFNとLLPのランドパターンは互換性がある場合も多く、一部のものはJEDECの規格で同じとされているが、DFNのピン数の多いものや小型サイズのものはJEDECの規格外のものが多く、互換性がない場合が多い。 DFNは多くのメーカーで使われているため、LLPと比べてサイズ・端子のバリエーションが非常に多い。

COB/COF/COG

[編集]COB(チップ・オン・ボード, Chip on board)は、ベア・チップをワイヤ・ボンディングもしくはフリップチップボンディングによってプリント基板上に直接実装する方法である。アンダーフィリングは行われる場合と、そうでない場合がある。主としてセンサー類の一次実装において用いられる。

COF(チップ・オン・フィルムまたはチップ・オン・フレックス, Chip on film, Chip on flex)は、COBの実装対象を硬質のリジット基板から、薄く柔軟なフレキシブル基板に換え、ベア・チップをフレキシブル基板にフリップチップボンディングにて実装したものである。主に液晶ドライバの接続に用いられる。

COG(チップ・オン・グラス, Chip on Glass)は、COFの実装対象をフィルム基板からガラス基板に換え、フリップチップボンディングによって直接実装したものである。かつてはワイヤボンディングも用いられた。携帯電話などの小型の液晶表示用ガラス基板にドライバICを実装するのに使用される。

WLCSP (Wafer Level Chip Scale Package)

[編集]ボンディング・ワイヤーによる内部配線を行なわず、半導体の一部が露出したままの、プリント基板上に単体の高集積度半導体を表面実装する時に最小限の占有面積で済ませられる半導体パッケージだが、面積が小さいので端子の数には限界があり、最近では、FOWLPと区別するためにFIWLP(Fan In Wafer Level Package)とも呼ばれる[4]。

FOWLP (Fan Out Wafer Level Package)

[編集]チップの端子から配線を引き出す再配線層を半導体工程で作り、外部端子につなげる。パッケージの面積が半導体チップ面積より大きく、チップの外側まで端子を広げること(fan out)ができるのでチップ面積と比べて端子数が多い用途でも採用できる[4]。

関連用語

[編集]リードフォーミング

[編集]リードフォーミングとは、実装する基板に適した形状にリードを曲げる加工のこと。主に個別部品のリード挿入型部品に対して行う。リードフォーミングが必要な場合、部品のメーカー側で需要者の要求に合わせて加工して納入することも多いが、需要者の側でフォーミングマシンを用意して加工することもある。部品パッケージの製造工程で端子を曲げる作業を指して使うこともある。

LLPは上の構造、DFNは下の構造である。

フリップ・チップ接続

[編集]フリップ・チップ接続(Flip chip bonding)とは、ダイをパッケージに実装する方法の1つで、ワイヤーボンディングとリードフレームを用いず、ダイの底面にあらかじめ形成しておいた接点をインターポーザーに直接はんだ付けするもの。製造方式として、ダイの配線層面の接続パッドにあらかじめはんだボールによるバンプを付けておき、チップを裏返して基板に実装する、IBMが開発したC4(Controlled Collapse Chip Connection)方式[5]と、ワイヤー・ボンディング用の金線でボンディング・ボールのみをダイの接続パッドに残置しておく金バンプ方式がある。C4方式では半田ボールとの間にアルミ再配線層やチタンやプラチナによるバリアメタル層が必要となり高コストであるため、金バンプ方式が一般的である。いずれもアンダー・フィル剤で基板とダイの間を埋めて固定する[6][注 26]。

CSP

[編集]CSP(Chip size package)は、内蔵する半導体チップと同じか少し大きめ程度の超小型パッケージの総称である。ダイをリードフレームまたはインターポーザー (Interposer) に実装し、ワイヤ・ボンディングかフリップチップによって接続する。端子はインターポーザー型ではBGAかLGAが多く、リードフレーム型ではLLP、DFNが使われる。端子間隔が0.8 mm以下のBGA形状かLGA形状のものはJEITAのパッケージ名称のFPGAかFLGAに分類される。また、BGAのものは、JEDECのパッケージ名称ではDSB (Die size BGA) に分類される。

ウエハーレベルCSP

[編集]ウエハーレベルCSP (Wafer level CSP) とは、ダイを切り分ける前のウエハーの状態で保護膜、端子、配線加工を行い、その後切り出す方式で作られるCSP。

COT

[編集]チップ・オン・テープ (Chip on tape, COT) は、ベア・チップの供給方法の1つであり、チップがテープに連続して貼り付けられ、リールに巻き取られた形態で需要者へ供給される。テープアンドリールのベア・チップ版である。

KGD

[編集]KGD(Known Good Die)とは、パッケージ化されていないダイの状態で検査され良品と判定された中間製品である。通常はパッケージ後に行なわれるバーンインといった出荷検査に合格した良品である事が保証されているダイであり、主にMCM用やSiP用に必要とされる。

MCP

[編集]MCP(Multi Chip Package)は、複数のベアチップを1つのパッケージ内に封入し、内部で配線を接続したものの総称である。内部で重ねられている場合と並べられている場合がある。重ねる場合には放熱に留意され、パッケージの薄型化が求められるものではダイを通常より多くバックグラインドしてメーカーによっては重ねられたもののみを指す場合がある。パッケージとしては通常のBGAやQFPなどの形をとるため、外観からはMCPであるかどうかの見分けが困難なものが多い。

MCM

[編集]MCM(Multi Chip Module)は、複数のベアチップを1つのパッケージ内に封入し、内部で配線を接続したもの。MCPの一種であるが、主にベアチップを2次元的に配置しボンディングワイヤーでチップ同士を配線したものを指す。パッケージサイズ/コストの面で3次元構造の方が優位とされる。

車載回路やRF回路などの信頼性や耐熱性が求められる分野では、セラミックス基板上にベアチップや受動素子を配置したものもある。アナログ回路が主である従来のハイブリッドICと呼ばれていたものに、ベースバンド処理やMCU等の比較的規模の大きいディジタル回路チップをセラミック基板上に混載したものである。[注 27]

SiP

[編集]SiP(System in Package)は、構造としてMCPとほぼ同義のものである。コンピュータシステムを例にとれば、従来はCPUやRAM/ROMなどをプリント基板上で個別に実装していたのに対し、1つのパッケージ内に複数のベアチップを内蔵しバンプなどにより結線を行うものであり、システム全体を1つのパッケージに収めたものという意味である。MCMと異なり3次元的にベアチップを重ねた構造を指すことが多い。積層配置は、ダイを貫通するビアを造らなくてはならない、ダイ裏面を薄く研磨加工しなければならない、高発熱のチップを混載する事ができないなど、技術的やコスト的な制約が多い。その為、MCMとSiPのそれぞれの特性を活かした、サブストレート基板にベアチップを水平配置する妥協案とも言える実装も多い。

A:SoCチップ B:フラッシュ・メモリー・チップ

1.インターポーザー/サブストレート 2.はんだボール 3.基板

PoP

[編集]PoP (パッケージ・オン・パッケージ, Package on Package) とは複数のサブパッケージを積層して基板上に実装すること。普通はインターポーザーを使用したサブパッケージ間をはんだボールによって接続される。実装面積を減らすとともに配線長を短縮でき、KGDも検査できる。

PiP

[編集]PiP (パッケージ・イン・パッケージ, Packege in Package) とはPoPが同方向に積層するのに対して、下層のサブパッケージを上下反対に取り付けたもの。例えばマイクロコントローラーとSRAMを1つのICにする場合、SRAMを上下反対(ハンダ面が上を向く)にしてその上にインターポーザーを介してマイクロコントローラーを乗せる。パッケージの中に両面基板が入っているような形態になる。PoPよりパッケージのピンを減らせるメリットがあるが、下層のサブパッケージに基板から直接電源を供給できない。

インターポーザー

[編集]

インターポーザー(Interposer)は上面にベア・チップを搭載し下面に端子を備えるプリント基板。従来のリードフレームとモールドの役割を兼ねる。サブストレートとも呼ばれ、主にマイクロプロセッサやチップセットでこの呼称が使われる[注 28]。

リード・フレーム

[編集]リード・フレーム(Lead frame)とはDIPパッケージなどのインターポーザを使用しないパッケージでリード端子とダイの保持を行なう金属板または金属線の集まりのこと。ダイの保持部分はグランド端子が担当する[7]。

ウインドウ

[編集]ウインドウ (Window) とはパッケージに窓が付いているもの。JEITAでは「D」で、JEDECでは「C」で表される。

シュリンク・ピッチ

[編集]シュリンク・ピッチ(Shrink pitch)とはJEITAとJEDECの分類の1つで、DIP、ZIP、PGA、SOPのパッケージで端子間隔が基本のものより狭いものをさす。SDIPは1.775 mm、SZIPは1.775 mmまたは1.25 mm、SPGAは1.27 mm、SSOPは1.00、0.80、0.65、0.50、0.40 mmをそれぞれ示す。「S」で表される。

ファインピッチ・パッケージ

[編集]ファインピッチ・パッケージとはJEDECとJEITAのパッケージ分類の1つで、BGAとLGAで端子間隔が0.8 mm以下のもの、又はQFPで端子間隔が0.5 mm以下のものを指す。記号「F」で表し、該当品はそれぞれFBGA、FLGA、FQFPと分類される。

ウルトラ・ファインピッチ・パッケージ

[編集]ウルトラ・ファインピッチ・パッケージ (Ultra fine pitch package) はJEITAとJEDECの分類の1つで、端子間隔が0.25 mm以下のパッケージのこと。

ベリー・シン・パッケージ

[編集]ベリー・シン・パッケージ(Very thin package)はJEITAとJEDECの分類の1つで、パッケージの基板上での取り付け高さが0.80 mm以上1.00 mm以下のパッケージのこと。

ベリー・ベリー・シン・パッケージ

[編集]ベリー・ベリー・シン・パッケージ(Very-very thin package)はJEITAとJEDECの分類の1つで、パッケージの基板上での取り付け高さが0.65 mm以上0.80 mm以下のパッケージのこと。

- ウルトラ・シン・パッケージ

- ウルトラ・シン・パッケージ (Ultra thin package) はJEITAとJEDECの分類の1つで、パッケージの基板上での取り付け高さが0.50mm以上0.65mm以下のパッケージのこと。「U」で表される。

エクストリームリイ・シン・パッケージ

[編集]エクストリームリイ・シン・パッケージ(Extremely thin package)はJEITAとJEDECの分類の1つで、パッケージの基板上での取り付け高さが0.50 mm以下のパッケージのこと。「X」で表される。

スタックト・パッケージ

[編集]CSPのようなダイに近いサイズで複数のダイを積層(スタック)することで実装面積とパッケージ容積を極限まで減らそうとしたもの。フリップ・チップやCSPで使用されている技術を応用することで、幾層ものダイ同士を積層して上下間はTSVやワイヤ・ボンディングで結線する。ダイサイズよりかなり大きくなるが、TBGAを積層することでも実現できる。

ハンダ・ボール

[編集]BGAやフリップ・チップでの接続に微小な半球状のはんだが使われる。欧州でのRoHSによる鉛規制後は、無鉛ハンダの使用が求められるようになっている。

バンパー

[編集]

QFPパッケージなどの端子の曲がりやすいパッケージの四隅に付けられた端子保護のためのツノ状の部分。普通は本体と同じくモールド樹脂で作られる。バンプとも呼ばれる。

フライング・リード

[編集]TAB技術などでチッブと接続するのにインナーリードが弧を描いている部分。

その他

[編集]部品内蔵プリント基板

[編集]多層プリント基板の製造過程で基板内部に電子部品を埋め込む部品内蔵プリント基板[3]の使用が広がっている。埋め込まれる電子部品はプリント基板の配線層の間の樹脂内に埋められ、はんだ付けやめっきで部品の端子と配線パターンが接続される。電子機器の回路基板として使用されるが、電子部品、特にICのパッケージングとして使用し、ある程度の回路をモジュール化したSiP(System In Package)の基板として使われることが多い。

脚注

[編集]注釈

[編集]- ^ 高機能なデジタル半導体の多くが良好な放熱を必要としており、それらのパッケージは多数の接続端子を備えたりヒートスプレッダを内蔵したりして、放熱特性の向上が図られている。また、電力制御用の半導体素子や高輝度照明用LED素子などでは、放熱板への取り付けを前提としたねじ穴や切り欠きが備わっている。

- ^ はんだに含まれる鉛が環境問題となるため鉛フリーはんだが求められ、その他の電子部品特有の有害物質も排除や削減が求められている。

- ^ 特殊な課題としては、微細化したデジタル半導体の中にはパッケージ中の放射性物質から放射される中性子によってソフトエラーを起こすため、この削減のためにパッケージ材料の純度を上げることで放射性物質の排除が求められる。

- ^ 例えば表面実装用アルミ電解コンデンサは、挿入用のアルミ電解コンデンサのリードを短く切って断面が平たくなるように潰し、台座に通してリードを内側に曲げたものが一般的である。

- ^ トランジスタなどで鉄製の端子が使われることもあった。

- ^ このため、放熱器を取り付けるときは絶縁する必要があり、各パッケージ用の絶縁シートが市販されている。

- ^ 金属缶パッケージと同様に絶縁の必要があるが、放熱性を犠牲にして金属板をプラスチックで覆って絶縁してあるものもあり、これはフルモールド型という。

- ^ タンタル電解コンデンサやマイカコンデンサ等のパッケージにも「ディップ」と呼ばれるものがあるが、これは樹脂に「漬けた(dip)」パッケージという意味で、ICのDIPパッケージとは全く関係ない。また、半導体のDIPと同じような形状の「DIPスイッチ」(ディップスイッチ)というものがあるが、こちらは半導体パッケージのDIPに由来する。

- ^ 過去には"DIL"とも呼ばれたことがあり、その外形から今でも俗称として「ムカデ」や「ゲジゲジ」と呼ばれる。

- ^ 一般にTTLと呼ばれるDIP形状の半導体製品の端子間隔は、米国の軍用規格に由来する"mil"(ミル)と呼ばれる1000分の1インチの長さを基準に定められた経緯があり、一般的なDIPでの最小端子間隔は100mil=2.54mm、2列の間隔は300mil=7.62mmであった。21世紀の今日ではデジタル半導体の接続端子数が増え、基板上での占有面積を小さくするためにピン間隔は狭くなる傾向がある。ピン間隔が2.54mmというデジタル半導体のパッケージは試作用途を除いて徐々に市場から姿を消しつつある。

- ^ パッドを上面や底面に出したトップブレイズドDIP、ボトムブレイズドDIPも存在するが、現在では非常にまれな存在である。

- ^ C-DIPと表現されている場合、ほとんどがセラミック・ディップではなくサー・ディップである。

- ^ パッケージ素材としてのセラミックはプラスチックに比べて、今でも放熱性が求められる製品で使用されることが多い。DIP形状でセラミックの使用割合が減っているのは、8~20ピン前後のICの多くがあまり発熱しない傾向があるためと考えられる。

- ^ P-DIPが登場してもしばらくは、Cer-DIPがEEPROMの消去用紫外線を透過させる石英ガラス窓を上面に設けたものでは、一般的なパッケージだった。

- ^ 素材がプラスチックでは出荷後の使用環境が高湿度であれば内部にゆっくりと水分が浸透するため、出荷後1年から数年ほどで内部の金属が腐食して機能しなくなることがある。このため高コストをいとわず高信頼性を求める製品ではセラミック素材が選ばれる。

- ^ DIPに限らずセラミックのパッケージではダイを強固にセラミック上に固着させると温度変化によって膨張・縮小した時に互いの膨張係数が大きく異なるためにダイが断裂する場合がある。これはCSPでも強固なサブストレートに固着させると同様であり、対策としてこれらの間には銅や高分子化合物などの緩衝材を入れて温度変化による変形を受け止めるようになっている。

- ^ MIL規格では「0.1インチ = 2.54mm = 100MIL」を長さの基本単位としていたため、21世紀に入って広がっている微小な表面実装用部品でのミリ単位の基準を除けば、デジタルICでの尺度の多くに今でもこの2.54mmの基準が残っている。

- ^ DIPと同様、発熱の大きい用途には放熱性が優れるCPGAが使用されていたが、後にPPGAやFC-PGAにヒートスプレッダと呼ばれる金属製の導熱板が付くようになり、放熱性におけるCPGAの優位性は薄れた。コスト的にもCPGAは不利であったため、現在ではCPGAはあまり使われなくなったがAMDは2011年現在もSocket_AM3などにPGAを使用している

- ^ ピン挿入型では不可能だった部品の両面実装が可能であり、それだけでも実装密度が向上する。さらに部品とそれを載せる基板上のはんだランドが小さいため、基板上の占有面積(フットプリント)が小さくできる。一般に基板のコストは配線層数と面積に比例するため、表面実装は基板コストを削減し、さらに筐体コストのような他のコスト削減にも寄与する。また、部品や接続端子の小型化や配線長の短縮は高周波回路における動作特性の向上に寄与する。一方、実装の過密化や配線幅の細線化が進むと、発熱の問題から特に高消費電力の部品の実装が難しくなり、適切な設計をしなければ部品の寿命を縮め製品不良の原因となる。また、回路故障時の修理や部品交換が難しくなる。

- ^ DRAMでLOCが一般的になったのは、16MBの世代からである。

- ^ トレイの移し替え時には、専用のエアーピンセットを使用してパッケージ本体上面だけで吸い上げるが、それでも曲げてしまうことがある。

- ^ LQFPは1.4mm程度、TQFPは1.0mm程度の厚みとなり、HQFPでは元のQFPと同等かより厚い3mm強となる。LQFP、TQFP、HQFPのリードピッチには 0.4、0.5、0.65mm や中には0.80mm のものなどいくつか存在する。

- ^ 近年は、DFNパッケージの4辺に端子を持つタイプのものが新たにQFNと呼ばれるようになっている。

- ^ TCPは基本的にフリップチップで、シリコンとヒートシンクを直接密着させた最初のパッケージ形態である。

- ^ 例外的にLLPと同じ構造の場合もある。

- ^ インテルが開発したBBUL(Bumpless build-up layer)は、それまでのC4のバンプ接続層を省略して、ダイをサブストレート基板に直接装着するパッケージである。これで接続端子の高密度化、20 GHz以上の導通が可能な低インダクタンス、1 mm厚のサブストレートを実現した。

- ^ MCP/MCMの1種に、以前からハイブリッドICと呼ばれるものがある。ハイブリッドICではICチップや多数の個別部品を基板上に実装してカバーで覆ったものであり、古典的なSiPともいえる電子部品である。また、フレキシブル基板をサブストレートとして使用して、2個や3個、又はそれ以上のダイを実装して折り畳むことでCSPに近いサイズのMCMとするものもある。この方式では折り畳む前に信号接続が可能なのでKGDの検査が行え、パッケージ完成前に不良品の交換が可能になる。

- ^ インターポーザーは非常に薄いプリント基板を極めて多数重ね合わせてある、周辺LSIとの接続性を確保する配線でもある。米intelのLGA2011用インターポーザーは重ね合わせてあるプリント基板を剥して1枚1枚並べるとテニスコート1面分にも及ぶ広大かつ複雑な回路になっている。

出典

[編集]- ^ 「システムLSIのできるまで」編集委員会編著、『システムLSIのできるまで』、日刊工業新聞社、2002年12月10日初版発行、ISBN 4526050482

- ^ a b c 菊池正典著 『半導体のすべて』、日本実業出版社、2006年8月10日初版発行、ISBN 4534041098、166-168頁

- ^ a b c 沼倉研史、E. Jan Vardaman著 『半導体パッケージのできるまで』、日刊工業新聞社、2005年12月12日初版1刷発行、ISBN 4526055581

- ^ a b Apple採用で業界騒然、FOWLP本格量産へ

- ^ 水野文夫、鷹野致和著 『半導体がわかる本』 オーム社 2006年6月20日第1版第1刷発行 ISBN 4274202534

- ^ 菊地正典監修 『半導体製造装置』 日本実業出版社 2007年4月20日初版発行 ISBN 9784534042170

- ^ 日経エレクトロニクス 2007年11月26日号 増刊「半導体パッケージ 各社独自名称が乱立, 整理して間違いを防ぐ」 p.129-p.139