閾値電圧

閾値電圧(しきいちでんあつ、Vth、英語:Threshold voltage、スレッショルド電圧、スレッシュホールド電圧)とは、デジタル信号を H(もしくは 1)/L(もしくは 0)信号として検知するのに必要となるしきい値となる電位のことである。仕組みを簡単に言うと、トランジスタをスイッチングさせるのに必要な電圧である。

電界効果トランジスタ(FET)を例とすると、ソース-ドレイン間の伝導パスを形成するために印加されるゲート–ソース間電圧VGS (th)にかかる電圧の事である。このように、トランジスタを内蔵しているICが信号として認識するのに必要な信号グランド間の最低限電位など色んな場所で使用される。この電圧は、電力効率や信号を維持するためには、最も重要な数字である。

接合型電界効果トランジスタ(JFET)における閾値電圧は「ピンチオフ電圧」と呼ばれることもあるが、これは若干紛らわしい言い方である。なぜなら絶縁ゲート電界効果トランジスタ(IGFET)において「ピンチオフ」とは、ソース-ドレイン間バイアスが大きい場合の電流飽和挙動を示すチャネルピンチオフのことを指し、このとき電流はゼロでは無いためである。「ピンチオフ」とは違い「閾値電圧」と言う言葉には曖昧さは無く、他の電界効果トランジスタにおいても同じ考えを表している。

なお、MOS型のFET(MOSFET)の閾値電圧については、MOSダイオードの「エネルギーバンド図」の項を参照されたい。

基本原理

[編集]nチャネル エンハンスメント形 デバイスでは、トランジスタ内に伝導チャネルが自然に存在せず、伝導チャネルを作るためには正のゲート-ソース電圧が必要である。正の電圧によって自由電子をゲートに引きつけ、伝導チャネルを形成する。しかしまずFETの基板に加えられたアクセプターイオンを中和するために十分な電子がゲート近くに引きつけなければならない。これは空乏層と呼ばれる移動キャリアが存在しない領域を形成する。これが起きる電圧を、FETの閾値電圧と呼ぶ。さらにゲート-ソース間電圧を大きくすると、より多くの電子がゲートに引きつけられ、ソースからドレインに伝導チャネルを作ることができる。これを「反転」と呼ぶ。

一方でnチャネル デプレッション形 デバイスは、トランジスタ内に伝導チャネルが自然に存在する。その結果「閾値電圧」という言葉はそのようなデバイスをオンするために用いられないが、その代わり電子が容易に流れることができるために十分なチャネル幅になる電圧のことを意味する。この流れやすい閾値はpチャネル デプレッション形 デバイスでも用いられる。ゲートから基板/ソースへの正の電圧が正孔をゲート-絶縁体/半導体界面から引き離すことにより空乏層を作り、キャリアが無く固定された負電荷のアクセプターイオンのみが存在する領域を作る。

幅広い平面のトランジスタにおいて閾値電圧はドレイン-ソース電圧に本質的に依存せず、よく定義された特徴がある。しかし現代のナノサイズMOSFETではドレイン誘起障壁低下によりあまり明確ではない。

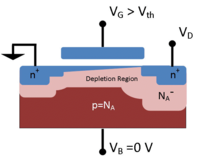

図では、ソース(図の左側)とドレイン(図の右側)は、高濃度にドープされたn領域(青)を示すため「n+」と記してある。空乏層(ピンク)ではイオンは負に帯電しており、正孔がほとんど無いことを示すため「NA−」と記してある。バルク(赤)では、正孔の数p = NAはバルク電荷を中性にする。

ゲート電圧が閾値電圧以下の場合(左図)、トランジスタはオフとなり、理想的にはトランジスタのドレインからソースへは電流は無い。実際は閾値電圧以下のゲート電圧でも小さい電流は存在し(サブスレッショルド電流)、ゲート電圧について指数関数的な変化する。

ゲート電圧が閾値電圧以上の場合(右図)、トランジスタはオンとなり、酸化膜-シリコン界面でのチャネルに多くの電子が存在するため、ドレインからソースへ電荷が流れることができる抵抗が小さいチャネルが作られる。閾値電圧を大きく上回る電圧では、この状況は強く反転していると呼ばれる。VD > 0の場合、チャネルは先細になる。なぜなら抵抗チャネルの電流による電圧降下は、ドレインに近づくにつれてチャネルを支える酸化物の電場を減少させるためである。

基板効果

[編集]基板効果とは、ソース-バルク電圧の変化にほぼ等しい大きさだけ閾値電圧が変化すること。(ソースは関係しない場合)基板が閾値電圧に影響するために起こる。基板は第二のゲートと考えることができるため「バックゲート」と呼ばれることもある。また基板効果は「バックゲート効果」と呼ばれることもある[1]。

エンハンスメントモードNMOS MOSFETでは、閾値電圧の基板効果はShichman–Hodgesモデルで計算でき[2]、以前のプロセスノードでは正しく[要説明]、次の方程式を用いる。

ここでは基板バイアスが存在する場合の閾値電圧、はソース-基板バイアス、は表面ポテンシャル、は基板バイアスがゼロの場合の閾値電圧、は基板効果パラメータ、は酸化膜厚、は酸化膜の誘電率、はシリコンの誘電率、はドーピング濃度、は電気素量である。

酸化膜厚の依存性

[編集]90 nmCMOSプロセスなどのテクノロジーノードでは、閾値電圧は酸化膜の種類と酸化膜厚に依存する。上述の基盤効果の式を用いると、はとに比例し、これは酸化膜厚のパラメータである。

よって酸化膜厚が薄くなると、閾値電圧は小さくなる。これは改良のように見えるが、代償が無いわけではない。酸化膜厚が薄くなれば、デバイスのサブスレッショルド電流も大きくなる。その結果、90nmゲート酸化膜厚の設計仕様は、リーク電流を制御するために1 nmとする[3]。この種のトンネル効果はFowler-Nordheimトンネル効果と呼ばれる[4]。

ここでとは一定で、はゲート酸化膜中の電場である。

設計構造が90 nm以下となる前は、酸化膜厚を作るデュアル酸化膜アプローチがこの問題の一般的な解決法であった。90 nmプロセス技術では、トリプル酸化膜アプローチが一部で適用された[5]。1つの標準酸化薄膜がトランジスタの大部分で使われ、別のものはI/Oドライバーセルに、さらに別のものはmemory-and-passトランジスタセルに用いられた。これらの違いは、CMOS技術の閾値電圧上の酸化膜厚の特性にのみ基づいている。

温度依存性

[編集]酸化膜厚が閾値電圧に影響するのと同様に、温度もCMOSデバイスの閾値電圧に影響する。基板効果の式の一部を展開すると、

ここでは接触電位の半分、はボルツマン定数、は温度、は電気素量、はドーピングパラメータ、は基板の真性キャリア濃度である。

表面ポテンシャルは温度と直接的な関係であることがわかる。上を見ると、閾値電圧は直接的な関係はもたないが、しかし効果に無関係ではない。この変化はドーピングレベルに依存して一般的に−4 mV/Kと−2 mV/Kの間である[6]。30 °Cの変化では、これは90 nmテクノロジーノードで一般的に用いられる500 mV設計パラメータから大きく変わる。

ランダムドーパントゆらぎの依存性

[編集]ランダムドーパントゆらぎ(RDF)は、注入された不純物濃度の変動によるある種の過程の変動である。MOSFETにおいてチャネル領域のRDFは、トランジスタの特性、特に閾値電圧を変える。新しいプロセス技術において、RDFはより大きな効果を持つ。なぜならドーパントの総数は、少ないためである[7]。

同じ製造プロセスを経験したデバイス間の閾値電圧の変動につながるドーパント変動を抑制するための研究が行われている[8]。

出典

[編集]- ^ Marco Delaurenti, PhD dissertation, Design and optimization techniques of high-speed VLSI circuits (1999) Archived 2014-11-10 at the Wayback Machine.

- ^ NanoDotTek Report NDT14-08-2007, 12 August 2007

- ^ Sugii, T.; Watanabe, K.; Sugatani, S. (2003). “Transistor Design for 90-nm Generation and Beyond”. FUJITSU Sci. Technol. J. 39 (1): 9–22.

- ^ S. M. Sze (1981). Physics of Semiconductor Devices (2nd ed.). New York: Wiley and Sons. pp. 496–504. ISBN 978-0471056614

- ^ Anil Telikepalli (2005年11月23日). “Power considerations in designing with 90 nm FPGAs”. EETimes. 2019年1月18日閲覧。

- ^ Weste and Eshraghian (1993). Principles of CMOS VLSI Design : a systems perspective (2nd ed.). pp. 48. ISBN 0-201-53376-6

- ^ Asenov, A. (1998). “Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFET's: A 3-D "atomistic" simulation study”. IEEE Transactions on Electron Devices 45 (12): 2505–2513. doi:10.1109/16.735728.

- ^ Asenov, A.; Saini, S. (1999). “Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1-μm MOSFET's with epitaxial and δ-doped channels”. IEEE Transactions on Electron Devices 46 (8): 1718–1724. doi:10.1109/16.777162.

関連項目

[編集]外部リンク

[編集]- Online lecture on: Threshold Voltage and MOSFET Capacitances by Dr. Lundstrom