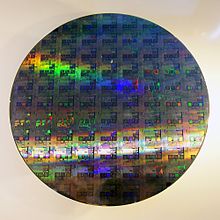

シリコンウェハー

シリコンウェハー(英: silicon wafer) は、高純度な珪素(シリコン)のウェハーである。シリコンウェハーは、珪素のインゴットを厚さ1 mm程度に切断して作られる。

シリコンウェハーは集積回路 (IC、またはLSI)の製造に最も多く使用される。このウェーハにアクセプターやドナーとなる不純物導入や絶縁膜形成、配線形成をすることにより半導体素子を形成することができる。

大口径化

[編集]ウェハー1枚あたりに取れるチップの数が多ければ低コスト化に繋がるため、インゴットの直径は大口径化が進んでいる。MOSデバイス用には150 mm(6インチ)、200 mm(8インチ)、300 mm(12インチ)のものが一般的に使用される。ダイオード等のチップサイズの小さなものには未だに100 mm(4インチ)、125 mm(5インチ)のものも使われている。基本的にチップサイズの大きなMPUや、大量に生産してコストを低減する必要のあるメモリ(DRAMやフラッシュメモリ)には大口径のウェーハが使用され、300 mm化の進展も著しい。

また近年は450 mmのシリコンウェハーを開発する動きがあり、半導体メーカー数社によるコンソーシアム「G450C」も作られている。また一方で、450 mm化してもその開発コストを回収できるのか懸念する動きも見られる。

種類

[編集]半導体デバイス用シリコンウェーハとしては、鏡面加工したPolished Wafer (PW) が使われるが、その内容を細かく見るとPWの中でも結晶欠陥COP (Crystal Originated Particle) の密度によっていくつかの水準に分けられるほか、Epitaxial Wafer(エピタキシャルウェーハ)、Anneal Wafer(アニールウェーハ)などいくつかのバリエーションがあり、コスト、特性を勘案してデバイス製造に用いられている。

製造工程

[編集]ここではシリコンウェハーの一般的な製造工程を記す。

大まかな流れ

[編集]現在のシリコンウェーハの大部分はCz法によって製造されているため、Cz法の大まかなプロセスを示す。

- 結晶成長プロセス

- シリコン融液→種結晶からの成長→ネッキングによる結晶無転位化→径制御→直胴部形成→ボトム形成→メルトからの切り離し→冷却→方位&径加工→ブロック切り出し

- ウェーハ加工プロセス

- スライス→面取り→ラップ→エッチング→ドナーキラー→精面取り→研磨

- 工程間には汚れを取り除くため、RCA洗浄をベースにした各種洗浄が用いられる。

シリコン精製

[編集]ノルウェーやブラジルで産出した純度の比較的高い石英を還元して、純度98 %程度の金属シリコンを作る。これを粉砕して塩素ガス、次いで水素ガスと反応させて、モノシラン (SiH4) やトリクロロシラン (SiHCl3) を作る。この過程で金属性の不純物はAlCl3やFeCl3のような塩化物として蒸発させトリクロロシランと分離することで金属性の不純物を1 ppba (parts per billion atomic) 以下まで取り除く。トリクロロシランは高純度の水素と CVD装置中に導入することで単体のシリコンを析出させ、高純度の多結晶シリコン・ロッドを得る[1][2]。

単結晶成長

[編集]高純度多結晶シリコン・ロッドは砕いて粗い粒状とし、一度洗浄した後、チョクラルスキー法(Czochralski法、Cz法)、又は、フローティングゾーン法(Floating Zone法、FZ法)によって単結晶のインゴットが作成される。

Cz法

[編集]

材料となる粗く砕かれた高純度多結晶シリコンは、石英のるつぼに詰められる。この段階で最終的な半導体の特性を決める微量の導電型不純物である、P型ならホウ素 (B) を、N型ならリン (P) やアンチモン (Sb) を加えておく。石英るつぼは不活性ガスで満たされた炉内に納められると、周囲からカーボンヒーターで加熱されて多結晶シリコンはやがて溶融する。溶けたシリコン液相表面の温度は溶解温度となるように厳密に管理され、その表面中心にピアノ線で吊るされた種結晶を接触させた後、ゆっくりと回転させながら引き上げていく。種結晶が接触した下部ではわずかに冷やされたシリコンが固体となって析出し種結晶の結晶配列を引き継いで溶解シリコン表面との間に成長してゆく。溶解シリコンから引き上げて成長させる過程で、引き上げ速度を少し上げたり溶解シリコンの温度を少し上げると結晶径が減少し、その逆は結晶径が拡大する。

種結晶はそれまでに作ったシリコン単結晶の残余であるが、内部に原子配列の転位が含まれている可能性があるため、下に成長してゆくシリコンへこの乱れが引き継がれないように「種しぼり」(ネッキング)と呼ばれる意図的に3 – 5 mm程度まで細くした部分を作る。この種しぼりによって結晶に転位が存在していても熱拡散によって転位が上方に移動するので無転位となる。また、結晶欠陥は転位が表面に移動することで結晶界面のエネルギーを減じることも欠陥が排除されることになる。種しぼり後は、るつぼの温度を下げて溶解シリコンを過冷却状態にする。望む口径のインゴットとなるように、溶解シリコンの温度、引き上げ速度、回転数を調整しながらゆっくりと回転させて引き上げていく。2000年代後半現在最新の直径300 mmインゴットは重さ350 kgにもなる。

石英製るつぼの表面から溶解シリコン中に酸素が混入するが、多くがSiOとして融解シリコン表面からガスとなって蒸発し炉壁などに付着して微粒子となる。この微粒子が再び融解シリコン表面に落下して結晶内に取り込まれると転位結晶となるため、炉の上部からアルゴンガスを導入して真空ポンプで吸引しSiOガスを排除することでこの影響を小さくする。また、炉壁から対流によって直接、結晶中に取り込まれる酸素を少なくするために、超伝導電磁石による静磁場を炉内に印加して溶解シリコン内の対流を抑制するMCZ法(Magnetic CZ法)が使われる[1]。また、融解シリコンから出たSiOガスが炉内のヒーターとして使われるグラファイトと反応してCOやCO2が発生している。これを放置すると融解シリコンに溶け込み結晶中に取り込まれて炭素濃度を高めることになるのでこのためにもアルゴンガスで排気されている[2]。偏析係数が1より小さい炭素 (0.07) や窒素 (7×10-4) 、ホウ素 (0.8) 、リン (0.35) といった不純物の濃度は結晶の成長に従って石英るつぼ中の融解シリコン液の減少により徐々に濃くなるため、結晶成長初期より終期の方が結晶中に取り込まれる不純物の濃度は高くなる。偏析係数が1より大きい不純物はこの逆の効果が起きる。酸素の偏析係数が1より大きいか小さいかは結論が出ていない。ドーパントとしてリンよりホウ素が選ばれるのは偏析による偏りが比較的小さいためである。

CZ法は大口径の単結晶が作りやすく、2000年代現在では量産半導体で使用される[100]方位の大口径ウェハー用の単結晶インゴットは、すべてこの方法により作られている。例外として結晶の成長方向にそって抵抗率の変化が大きいという問題により、パワーデバイスにはあまり用いられない。

FZ法

[編集]多結晶シリコンのインゴットを部分的に溶融しながら単結晶化を行う方法でゾーンメルト法の一種。結晶の成長方向の不純物分布が一定であり、また酸素濃度が非常に少ないという利点があるが、結晶の半径方向の抵抗率分布にばらつきがあるため、中性子照射により抵抗率の均一化が図られる。

加工

[編集]ブロック切断・外周研削

[編集]インゴットの両端部(トップとテール)を切断し外周を研削して、長い物は適切な長さで切断され所定の直径を持った長さ30 cm – 50 cmの円柱状の「ブロック」を作る。

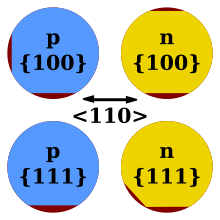

方位加工

[編集]

X線方位測定によって結晶方位を測定し、後の工程で方位が判るように所定の位置に「オリエンテーションフラット」 (orientation flat; OF) 又は「ノッチ」を刻み込む[1]。

スライシング

[編集]ブロックをカーボン台に接着してから、ダイシングソー、ワイヤーソー、又は内周刃ブレード[1] (ID‐Saw) でウエハー状に切り出す。直径300 mmのブロックは、通常、マルチ・ワイヤーソーによって1度に最大200枚の切断が行なわれる[2]。

ベベリング

[編集]シリコンは固くてもろく、ウエハーの端面がスライシング時の鋭利なままでは、続く処理工程での搬送や位置合わせなどの取り扱い時に容易に割れたり欠けたりして、断片がウエハー表面を傷つけたり汚染したりする。これを防ぐため、ベベリング工程では切り出されたウエハーの端面をダイヤモンドでコートされた「面取り砥石」で面取りする。

ラッピング工程の後に行なわれることもある[1]。

この時、バラツキのある外周の直径を合わせ、オリエンテーションフラット (OF) の幅の長さを合わせる事や、ノッチと呼ばれる微少な切り欠きの寸法を合わせる事も含まれる。ベベリング工程で使用される装置はベベリングマシンと言われ、日本メーカーの東精エンジニアリングの装置が、特に300㎜シリコンウェハーの市場で多くのシェアを占めている。

ラッピング

[編集]ラッピング工程では、鋳物製の上下2枚の定盤間にウエハーとステンレス製キャリアを挟み込み、そこにアルミナかシリコンカーバイドの砥粒を含んだラップ液を流し込みながら擦り合わせて、スライシング工程の時にできた表面の凹凸を除去しながら厚さ揃え、また表裏面の平行度も高める。

キャリアは、求めるウエハー厚よりやや薄い、外周にギアを持つドーナツ状のステンレス板であり、ギアによって周囲から回転が与えられドーナツ内に収まったウエハーに回転運動を伝える[1]。

エッチング

[編集]エッチング工程ではそれまでに残ったウエハー表面の微細な凹凸を化学研磨によってさらに平滑にする。フッ酸 (HF) と硝酸 (HNO3) を純水か酢酸 (CH3COOH) で薄めた酸性エッチング液を使うものと、水酸化カリウム (KOH) と水酸化ナトリウム (NaOH) を純水で薄めたアルカリ性エッチング液を使うものとがある。アルカリ性の方が主体となる[1]。

ドナーキラーアニーリング

[編集]CZ法やMCZ法によって単結晶を製造すると石英るつぼから溶け込んだ酸素原子が高温状態によって互いに集合する。CZ法では酸素原子が1018個/cm3程も溶け込む。

この酸素原子のかたまりは電子を放出するドナーとなることで、局所的に電子の通過を阻害し電気的には抵抗となる。これによりドーパントで制御された抵抗値からずれるため、このドナーとなった酸素原子を分散させるための熱処理がドナーキラーアニーリング加工である。この工程ではウエハーを不活性ガス中で600–700℃に短時間加熱する。この処理は加工応力の緩和や結晶欠陥の低減等も兼ねる[1]。

エッジポリッシュ

[編集]ベベリング工程による機械的な研磨だけではウエハー端部のベベル面がまだ粗く、プロセスルールの微細化やウエハーの大口径化によって端部が治具等との接触で生じるわずかな塵の発生も見逃せなくなっている。エッジポリッシュ工程ではウエハーの端部(エッジ)を機械的化学的研磨 (CMP) によって鏡のように滑らかにする[1]。

ポリッシング

[編集]ポリッシング工程では最終的なプロセス加工面を作るために、200 mmウエハーまでは多くが片面のみに対して機械的化学的研磨 (CMP) によって極めて平滑な鏡面状態とする。300 mmウエハーからは国際標準で片面だけでなく裏面も表面の80–100 %程度の精度にまで平滑な鏡面状態となるように研磨して、表面への平滑度の影響を最小にしている。

例えば、100 nmのプロセスルールではステッパによる露光に精度が求められるために、100 nm以下のローカルサイト平坦度が求められる。

この研磨工程ではウエハーを回転する円盤状の大きな研磨テーブルに何枚か並べて接着し、これらのウエハーの上面を小さめの回転円盤である研磨定盤に付けられた研磨クロスで上から研磨する。同時にコロイダルシリカが含まれるアルカリ性研磨液をこれらの間に流動するように流し込み、機械的研磨と化学的研磨を同時に行なう[1]。

主にポリッシング工程によって表面でも使用できない端面除外領域 (Edge Exclusive Area, EEA) とよばれる外周端近く2 mm程度のドーナッツ状の領域が生まれる。これは研磨が外周部でより進む結果、最外周で数百μm程度まで過度に研磨されこの領域が傾斜をもって薄くなるためである。このEEAの内側がFQA (Fixed Quality Area) と呼ばれる使用が可能な領域である[2]。

高品質加工

[編集]より表面欠陥密度の低い高品質のウエハーを求める要求に応じてさらに加工が行なわれ、エピタキシャル・ウエハー (Epitaxial wafer) とアニール・ウエハー (Annealed wafer) 、そして特殊な要求に応じたものとしてSOIウエハー (Semiconductor On Insulator wafer, Silicon On Insulator wafer) が作られる。これらの加工を行なわないものはポリッシュッド・ウエハー (Polished wafer, PW) と呼ばれる。

エピタキシャル・ウエハーはシリコン単結晶層を気相成長で数μm堆積したものである。この過程でボロンを10―19cm3程度添加するP+ウエハーがある。

アニール・ウエハーはアルゴン雰囲気中で1150 – 1200度程度に加熱して表面近くの酸素を追い出す。窒素を加えるアニールもある[2]。

洗浄

[編集]洗浄工程ではこれまでの工程でウエハーに付いた汚れを洗浄する。米RCA社 (Radio of Corporation of America Corp.) で開発された「RCA洗浄法」という化学的洗浄法を基本にしている。RCA洗浄法では次の2段階の洗浄を行なう。

- SC1 (Standard Clean 1)

- 水"5"に対して、過酸化水素 (H2O2) "1"と水酸化アンモニウム (NH4OH) "1"の高pHのアルカリ性混合液

- SC2 (Standard Clean 2)

- 水"5"に対して、塩酸 (HCl) "1"と過酸化水素 (H2O2) "1"の低pHの酸性混合液

SC1で有機物汚染を除き、SC2でアルカリイオンやAl3+やFe3+といった陽イオンの除去を行なう[1]。

検査・梱包

[編集]結晶特性と外観を検査した後、梱包されて出荷される。結晶特性の検査には、結晶方位、導電型、抵抗率、結晶欠陥、炭素と酸素の濃度があり、外観の検査では、反り、平坦度、汚れ、傷が検査される。

梱包のケースは、従来多種類だったウエハーの格納ジャーが、FOUP (Front Opening Unified Pod) という国際規格の制定後は、共通のウエハー用格納ポッドで扱えるようになっている[1]。

メーカー

[編集]シリコンウェーハの大手ベンダーには日系メーカーが多く、全体に占める日系のシェアは60 %を超える。最大手は信越半導体、二番手はSUMCOである。以下、MEMC(米)、Siltronic(仏)、グローバルウェーハズ・ジャパン(日)、LG Siltron(韓)などが大手で、それ以外にも比較的小規模なメーカー、再生ウェーハ専門、SOIウェーハ専門など、特徴を持ったメーカーがある。

SOITEC(仏)は次世代デバイス用(高速、低消費電力を狙ったMPUなど)に使われる薄膜SOIウェーハでは、代表的なメーカーである。

出典

[編集]関連項目

[編集]- 電子部品

- ダイシングソー

- 電子立国日本の自叙伝 - 1991年にNHKスペシャル枠で放送されたドキュメンタリー番組。第1回放送でシリコンウェハーの製造過程を詳細に捉えている。