四倍精度浮動小数点数

四倍精度浮動小数点形式(よんばいせいどふどうしょうすうてん、英語: quadruple-precision floating-point format)は、浮動小数点数の形式の1つで、よく使われている通常の倍精度形式と比して、仮数部の長さが約2倍である。

Nicholas J. Higham『Accuracy and Stability of Numerical Algorithms』(2nd.e)が、カハンの言として引用している文によれば、

For now the 10-byte Extended format is a tolerable compromise between the value of extra-precise arithmetic and the price of implementing it to run fast; very soon two more bytes of precision will become tolerable, and ultimately a 16-byte format ... That kind of gradual evolution towards wider precision was already in view when IEEE Standard 754 for Floating-Point Arithmetic was framed.[1]

(訳)これまでのところは、10バイトの拡張倍精度は、高精度演算の価値と高速に動作させるための実装コストとの間の妥協点としては許容できるものです。そうしてすぐにさらに2バイト分長い精度が妥当になるでしょう。そうして究極的には16バイトフォーマットもが…。この種の、より広い精度への段階的な進化はIEEE 754の規格が形成された時には既に想定されていました。

とのことである。(編注: 英語版Wikipediaが孫引きしている。英語版Wikipediaの引用元が示している引用元は「W. Kahan. Computer benchmarks versus accuracy. Draft manuscript, June 1994.」となっている)

IEEE 754-2008では、128ビットの二進フォーマットが公式にbinary128として定義された。次に示す。

IEEE 754 四倍精度二進浮動小数点フォーマット: binary128

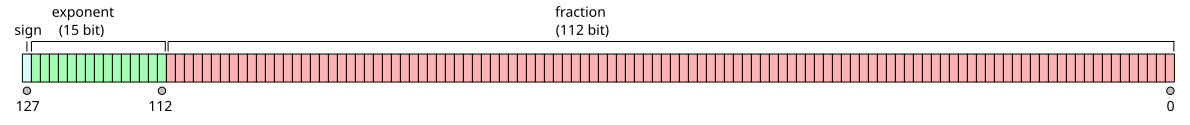

[編集]IEEE 754-2008は四倍精度二進浮動小数点フォーマットbinary128を以下のように定めている。

これは十進換算で33桁〜36桁に相当する(十進小数→binary128→十進小数のラウンドトリップが可能な最大桁数が33桁、binary128→十進小数→binary128のラウンドトリップが可能な最大桁数が36桁[2])。

このフォーマットは、正規化数の場合は最上位の1が暗黙のうちに存在するものとして省略される(いわゆるケチ表現)。これにより113ビット(十進換算約34桁: )の精度の仮数部の112ビットのみがメモリフォーマット上に現れる。ビットの配置は次のようになっている。

指数部

[編集]他の精度の場合と同様に、指数はゲタ履き表現(IEEE 754ではexponent bias)で、オフセットは16383である。特別な場合(後述)についても基本的に他と同様である。

- Emin = 000116−3FFF16 = −16382

- Emax = 7FFE16−3FFF16 = 16383

- バイアス = 3FFF16 = 16383

ゲタ履き表現なので、実際の指数を得るには、ビットパターンによる表現からオフセットの16383を引く。

指数部が000016と7FFF16の場合は特別な場合で、それぞれ、ゼロ・非正規数、無限大・NaNの表現である。

| 指数 | 仮数ゼロ | 仮数非ゼロ | 式 |

|---|---|---|---|

| 000016 | 0, −0 | 非正規化数 | |

| 000116, ..., 7FFE16 | 正規化数 | ||

| 7FFF16 | ±∞ | NaN (quiet, signalling) | |

値の範囲

[編集]最小の真に正の値(非正規化数)は2−16493 ≈ 10−4965であり、1ビットの精度である。 最小の正の正規化数は2−16382 ≈ 3.3621 × 10−4932であり、112ビットの精度がある。 最大の表現可能な値は216384 − 216272 ≈ 1.1897 × 104932である。

仮数部

[編集]TBD

例

[編集]ここでは十六進で表現する。符号、(バイアスされた)指数、仮数の、全てを含んでいる。

3fff 0000 0000 0000 0000 0000 0000 0000 = 1 c000 0000 0000 0000 0000 0000 0000 0000 = −2

7ffe ffff ffff ffff ffff ffff ffff ffff ≈ 1.189731495357231765085759326628007 × 104932 (最大の四倍精度浮動小数点数)

0000 0000 0000 0000 0000 0000 0000 0000 = 0 8000 0000 0000 0000 0000 0000 0000 0000 = −0

7fff 0000 0000 0000 0000 0000 0000 0000 = infinity ffff 0000 0000 0000 0000 0000 0000 0000 = −infinity

3ffd 5555 5555 5555 5555 5555 5555 5555 ≈ 1/3

デフォルトでは、1/3は倍精度と同様、切り捨てられる。これは仮数のビット数が奇数であるため、丸め位置以降のビット列が0101...となり、1/2ulpより小さいためである。

サポート

[編集]四倍精度をサポートする処理系やアーキテクチャについて述べる。

利用者数が極めて少ないためか、利用環境は整っているとは言い難い現状がある。まず、処理系の独自拡張としての実装は存在するが、標準の言語仕様では四倍精度が定義されていない(独自拡張は、可搬性(portability)が必要な場合は利用できない)。マイクロプロセッサのハードウェアサポートは、携帯端末用は無論パーソナルコンピュータ用やサーバ用を含めほとんどが、倍精度までであり、ソフトウェアによる処理は一般に数倍以上遅い。

一部の処理系や、64ビットアーキテクチャの場合にC言語で long double が128ビット(sizeof(long double) が 16)のことがあるが、単に拡張倍精度フォーマットを格納するのに16バイトを使うだけであることもある。また、オプションで切り替える場合はバイナリ互換性がなくなることがありうるので注意を要する。独自拡張で(最新のGCCなど) __float128 といった型が使えることもあるが、文字列表現との相互変換などのサポートが十分でないこともある。最近のGNU FORTRAN (gfortran) にはIEEE754の四倍精度のサポートがある。

IBMのアーキテクチャには、次節で述べるdouble-doubleの原理による四倍精度の扱いをサポートしているものがある。また、IBM Power9 (POWER ISA3.0)では、IEEE 754 の4倍精度FPと4倍精度十進FPをサポートした。

命令セットとしては用意があるがハードウェアでのサポートが無く、ソフトウェア実行になるというプラットフォームもある。たとえばSPARC-V9には四倍精度浮動小数点演算の命令があるが、2012年現在これをハードウェアで実装したSPARCの実機は無く、ソフトウェアで実行される。

専用計算機等での実装例の報告は少なくない。たとえばGRAPE-MPのように多倍長精度に特化した設計などもある。

(SSEでは128ビット長のレジスタを対象として浮動小数点演算を行うが、複数の単精度や倍精度演算を同時に行う機能のみで四倍精度演算のサポートはない。次節のdouble-doubleの実装に使用されることがある)

double-double演算

[編集]通常の倍精度浮動小数点形式のペアを用いて、四倍精度による処理を擬似的に実現する手法がある[3][4][5]。その手法を「double-double演算」などといい、またそれによって擬似的に実現されている四倍精度が「擬似四倍精度」などと言われることがある。

真の四倍精度計算とは異なり、仮数53ビットのIEEE倍精度数の1対を用いることで、double-double演算は少なくとも[3]2×53=106ビットの仮数(もしくは可能性としては符号ビットの巧妙な扱いにより107ビット[6])を実現する計算手法である。これはIEEEのbinary128の113ビットの仮数よりも7ビット短いだけである。一方、指数部は11ビットのままであるので、表現できる値の大きさの範囲は基本的に倍精度と同じである[3]。これは四倍精度の指数部が15ビットであることに比べて格段に劣る(double-doubleのに対し、binary128は)。 具体的には、double-double/四倍精度の値qをdouble-doubleの技術で表す場合、2つの倍精度数xとyの対を用いてq=x+yという和の形で表現する。この各々の仮数部はqの仮数部の上下半分ずつを持つ[4]。つまり、qの代わりに(x,y)という対で格納されており、qに対する演算(加減乗除等)はxとyに対する等価な(ただし複雑な)演算に変換される。これにより、四倍精度の演算は(複数の)倍精度の演算の組み合わせに還元される。倍精度演算は多くの場合ハードウェアとして実装されているため、double-double演算は通常は、一般の任意精度演算よりは十分に高速である[4][3]。 なお、double-double演算には次のような特徴がある[7]。

- 値の絶対値が減少すると、追加の精度も減少する。そのため、正規化数の範囲での最小の数は倍精度よりも狭い。完全な精度を持つ最小の数は1000...02 (ゼロが106個) × 2−1074、あるいは 1.000...02 (ゼロが106個) × 2−968である。

- 実際の精度は変化する。一般に、対の下位パートの絶対値は上位パートのULPの半分を超えない。下位パートが上位パートのULPの半分より小さいならば、上位と下位の仮数の間に黙示的な全0あるいは全1のビットが存在する。仮数のビット数が固定であることに依存するアルゴリズムは128ビット長の倍精度数を使うとき失敗する可能性がある。

- 上の理由により、1 + 2−1074のような値を表現する事ができる。これは1よりも大きい最小の表現可能な値である。

更に高い精度が要求されるならば、triple-double(159または161ビット精度)やquad-double(212または215ビット精度)演算を考えることもできる。

同様の手法で2つの四倍精度数からなるdouble-quad演算を考えることもできる。これは少なくとも226または227ビットの精度を持つ。[8]

八倍精度

[編集]四倍精度より精度が高く、任意精度演算より高性能な計算のためのフォーマットとして、6倍から8倍までの精度が検討されており[9][10]、いくつかの方式によるソフトウェアによる実装の報告[11][12][13][14]、GRAPE-MP 4/6/8の試作や、FPGAへの実装[12]といったハードウェアの報告などがある。

関連項目

[編集]- コンピュータの数値表現

- 浮動小数点数

- 半精度浮動小数点数 (16bit)

- 単精度浮動小数点数 (32bit)

- 倍精度浮動小数点数 (64bit)

- 拡張倍精度浮動小数点数 (80bit)

- 四倍精度浮動小数点数 (128bit)

- IEEE 754

注釈

[編集]- ^ ケチ表現

出典

[編集]- ^ Higham, Nicholas (2002). Accuracy and Stability of Numerical Algorithms (2 ed). SIAM. pp. 43

- ^ William Kahan (1 October 1987). “Lecture Notes on the Status of IEEE Standard 754 for Binary Floating-Point Arithmetic”. 2012年11月13日閲覧。

- ^ a b c d Yozo Hida, X. Li, and D. H. Bailey, Quad-Double Arithmetic: Algorithms, Implementation, and Application, Lawrence Berkeley National Laboratory Technical Report LBNL-46996 (2000). Also Y. Hida et al., Library for double-double and quad-double arithmetic (2007).

- ^ a b c J. R. Shewchuk, Adaptive Precision Floating-Point Arithmetic and Fast Robust Geometric Predicates, Discrete & Computational Geometry 18:305-363, 1997.

- ^ Knuth, D. E.. The Art of Computer Programming (2nd ed.). chapter 4.2.3. problem 9.

- ^ Robert MunafoF107 and F161 High-Precision Floating-Point Data Types (2011).

- ^ 128-Bit Long Double Floating-Point Data Type

- ^ sourceware.org Re: The state of glibc libm

- ^ KEK 「多倍長精度計算フォーラム」第2回研究会を開催

- ^ http://suchix.kek.jp/mpcomp/20111210-forum/mpcomp-forum.pdf 「多倍長精度演算の性能評価」(PDF)

- ^ http://www.apple.com/acg/pdf/oct3a.pdf "Octuple-precision floating point on Apple G4" (PDF)

- ^ a b https://cir.nii.ac.jp/crid/1572543026893254272 「高性能な8倍精度浮動小数点演算機構の実現」

- ^ http://id.nii.ac.jp/1001/00071791/ 情報処理学会電子図書館「GPUによる4倍・8倍精度BLASの実装と評価」

- ^ http://kaken.nii.ac.jp/d/p/21540123 「Web上での簡便な8倍精度数値計算システムの構築」

外部リンク

[編集]- High-Precision Software Directory

- QPFloat, a free software (GPL) software library for quadruple-precision arithmetic

- HPAlib, a free software (LGPL) software library for quad-precision arithmetic

- libquadmath, the GCC quad-precision math library

- IEEE-754 Analysis, Interactive web page for examining Binary32, Binary64, and Binary128 floating-point values

- IBM Advances Against x86 with Power9 (2016年8月30日 HPCwire記事)